Adder (electronics) 加法器(电子)

Digital circuit that produces sums from inputs

从输入产生和的数字电路 From Wikipedia, the free encyclopedia

来自维基百科,自由的百科全书

An adder, or summer,[1] is a digital circuit that performs addition of numbers. In many computers and other kinds of processors, adders are used in the arithmetic logic units (ALUs). They are also used in other parts of the processor, where they are used to calculate addresses, table indices, increment and decrement operators and similar operations.

加法器或夏号是执行数字加法的数字电路。在许多计算机和其他类型的处理器中,加法器用于算术逻辑单元 (ALU)。它们还用于处理器的其他部分,用于计算地址、表索引、递增和递减运算符以及类似的操作。

Although adders can be constructed for many number representations, such as binary-coded decimal or excess-3, the most common adders operate on binary numbers.

In cases where two's complement or ones' complement is being used to represent negative numbers, it is trivial to modify an adder into an adder–subtractor.

Other signed number representations require more logic around the basic adder.

尽管可以为许多数字表示形式构造加法器,例如二进制编码的 decimal 或 excess-3,但最常见的加法器对二进制数进行操作。在 2 的补码或 1 的补码用于表示负数的情况下,将加法器修改为加法器-减法器是微不足道的。其他有符号数字表示需要围绕基本加法器的更多 logic。

History 历史

George Stibitz invented the 2-bit binary adder (the Model K) in 1937.

George Stibitz 于 1937 年发明了 2 位二进制加法器(K 型)。

Binary adders 二进制加法器

Half adder 半加器

The half adder adds two single binary digits and . It has two outputs, sum () and carry (). The carry signal represents an overflow into the next digit of a multi-digit addition. The value of the sum is . The simplest half-adder design, pictured on the right, incorporates an XOR gate for and an AND gate for . The Boolean logic for the sum (in this case ) will be whereas for the carry () will be . With the addition of an OR gate to combine their carry outputs, two half adders can be combined to make a full adder.[2] The half adder adds two input bits and generates a carry and sum, which are the two outputs of a half adder. The input variables of a half adder are called the augend and addend bits. The output variables are the sum and carry.

半加器添加两个单个二进制数字 和 .它有两个输出,sum ( ) 和 carry ( )。进位信号表示多位数加法的下一位数字的溢出。sum 的值为 。最简单的半加器设计,如右图所示,包含一个 XOR 门和一个 AND 门。 sum 的布尔逻辑 (在本例中 ) 将为 ,而进位 ( ) 的布尔逻辑将为 。通过添加 OR 门来组合它们的进位输出,可以将两个半加器组合成一个完整的加器。半加器添加两个 input 位并生成 carry 和 sum,这是半加器的两个输出。半加器的 Importing 变量称为 augend 和 addend 位。输出变量是 sum 和 carry。

The truth table for the half adder is:

half adder 的真值表为:

| Inputs 输入 | Outputs 输出 | ||

|---|---|---|---|

| A | B | Cout C出 | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Various half adder digital logic circuits:

各种半加器数字逻辑电路:

- Half adder in action. 半加器在行动。

Full adder 全加器

A full adder adds binary numbers and accounts for values carried in as well as out. A one-bit full-adder adds three one-bit numbers, often written as , , and ; and are the operands, and is a bit carried in from the previous less-significant stage.[3] The circuit produces a two-bit output. Output carry and sum are typically represented by the signals and , where the sum equals . The full adder is usually a component in a cascade of adders, which add 8, 16, 32, etc. bit binary numbers.

全加器添加二进制数并考虑进出的值。一个 1 位全加器加上三个 1 位数字,通常写成 、 和 ; 和 是操作数,并且 是从上一个不太重要的阶段引入的。该电路产生一个 2 位输出。输出进位和总和通常由信号 和 表示,其中总和等于 。全加法器通常是 cascade 加法器中的一个组件,它添加 8、16、32 等位二进制数。

A full adder can be implemented in many different ways such as with a custom transistor-level circuit or composed of other gates. The most common implementation is with:

全加法器可以通过许多不同的方式实现,例如使用定制的晶体管级电路或由其他门组成。最常见的实现方式是:

The above expressions for and can be derived from using a Karnaugh map to simplify the truth table.

上述表达式 for 和 可以通过使用 Karnaugh 映射来简化真值表来推导出来。

In this implementation, the final OR gate before the carry-out output may be replaced by an XOR gate without altering the resulting logic. This is because when A and B are both 1, the term is always 0, and hence can only be 0. Thus, the inputs to the final OR gate can never be both 1's (this is the only combination for which the OR and XOR outputs differ).

在此 implementation中,执行输出之前的最后一个 OR 门可以替换为 XOR 门,而不会改变结果逻辑。这是因为当 A 和 B 都为 1 时,项 始终为 0,因此 只能为 0。因此,最终 OR 门的输入永远不能同时是 1(这是 OR 和 XOR 输出唯一不同的组合)。

Due to the functional completeness property of the NAND and NOR gates, a full adder can also be implemented using nine NAND gates,[4] or nine NOR gates.

由于 NAND 和 NOR 门的功能完备性,也可以使用 9 个 NAND 门或 9 个 NOR 门来实现全加法器。

Using only two types of gates is convenient if the circuit is being implemented using simple integrated circuit chips which contain only one gate type per chip.

如果电路使用简单的集成电路芯片实现,则仅使用两种类型的门是很方便的,每个芯片只包含一个门类型。

A full adder can also be constructed from two half adders by connecting and to the input of one half adder, then taking its sum-output as one of the inputs to the second half adder and as its other input, and finally the carry outputs from the two half-adders are connected to an OR gate. The sum-output from the second half adder is the final sum output () of the full adder and the output from the OR gate is the final carry output (). The critical path of a full adder runs through both XOR gates and ends at the sum bit . Assumed that an XOR gate takes 1 delays to complete, the delay imposed by the critical path of a full adder is equal to:

一个全加器也可以由两个半加器构建,方法是连接 和一个 半加器的输入,然后将其总和输出 作为第二个半加器的输入之一和 另一个输入,最后两个半加器的进位输出连接到一个 OR 门。来自后半加法器的和输出是全加器的最终和输出 ( ),来自 OR 门的输出是最终进位输出 ( )。全加法器的关键路径穿过两个 XOR 门,并在 sum bit 结束。假设 XOR 门需要 1 个延迟才能完成,则全加器的关键路径施加的延迟等于:

The critical path of a carry runs through one XOR gate in adder and through 2 gates (AND and OR) in carry-block and therefore, if AND or OR gates take 1 delay to complete, has a delay of:

进位的关键路径穿过加法器中的一个 XOR 门和进位块中的 2 个门(AND 和 OR),因此,如果 AND 或 OR 门需要 1 个延迟才能完成,则延迟为:

The truth table for the full adder is:

完整加法器的真值表为:

| Inputs | Outputs | |||

|---|---|---|---|---|

| A | B | Cin | Cout | S |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Inverting all inputs of a full adder also inverts all of its outputs, which can be used in the design of fast ripple-carry adders, because there is no need to invert the carry.[5]

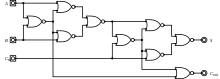

Various full adder digital logic circuits:

- Full adder in action.

- Schematic of full adder implemented with nine NAND gates.

- Schematic of full adder implemented with nine NOR gates.

- Schematic symbol for a 1-bit full adder with Cin and Cout drawn on sides of block to emphasize their use in a multi-bit adder

Adders supporting multiple bits

Ripple-carry adder

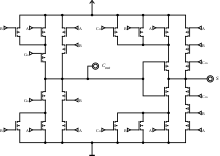

It is possible to create a logical circuit using multiple full adders to add N-bit numbers. Each full adder inputs a , which is the of the previous adder. This kind of adder is called a ripple-carry adder (RCA), since each carry bit "ripples" to the next full adder. The first (and only the first) full adder may be replaced by a half adder (under the assumption that ).

The layout of a ripple-carry adder is simple, which allows fast design time; however, the ripple-carry adder is relatively slow, since each full adder must wait for the carry bit to be calculated from the previous full adder. The gate delay can easily be calculated by inspection of the full adder circuit. Each full adder requires three levels of logic. In a 32-bit ripple-carry adder, there are 32 full adders, so the critical path (worst case) delay is 3 (from input to carry in first adder) + 31 × 2 (for carry propagation in latter adders) = 65 gate delays.[6] The general equation for the worst-case delay for a n-bit carry-ripple adder, accounting for both the sum and carry bits, is:

A design with alternating carry polarities and optimized AND-OR-Invert gates can be about twice as fast.[7][5]

Carry-lookahead adder (Weinberger and Smith, 1958)

To reduce the computation time, Weinberger and Smith invented a faster way to add two binary numbers by using carry-lookahead adders (CLA).[8] They introduced two signals ( and ) for each bit position, based on whether a carry is propagated through from a less significant bit position (at least one input is a 1), generated in that bit position (both inputs are 1), or killed in that bit position (both inputs are 0). In most cases, is simply the sum output of a half adder and is the carry output of the same adder. After and are generated, the carries for every bit position are created.

Mere derivation of Weinberger-Smith CLA recurrence, are: Brent–Kung adder (BKA),[9] and the Kogge–Stone adder (KSA).[10][11] This was shown in Oklobdzija and Zeydel paper in IEEE Journal of Solid-State Circutis.[12]

Some other multi-bit adder architectures break the adder into blocks. It is possible to vary the length of these blocks based on the propagation delay of the circuits to optimize computation time. These block based adders include the carry-skip (or carry-bypass) adder which will determine and values for each block rather than each bit, and the carry-select adder which pre-generates the sum and carry values for either possible carry input (0 or 1) to the block, using multiplexers to select the appropriate result when the carry bit is known.

By combining multiple carry-lookahead adders, even larger adders can be created. This can be used at multiple levels to make even larger adders. For example, the following adder is a 64-bit adder that uses four 16-bit CLAs with two levels of lookahead carry units.

Other adder designs include the carry-select adder, conditional sum adder, carry-skip adder, and carry-complete adder.

Carry-save adders

If an adding circuit is to compute the sum of three or more numbers, it can be advantageous to not propagate the carry result. Instead, three-input adders are used, generating two results: a sum and a carry. The sum and the carry may be fed into two inputs of the subsequent 3-number adder without having to wait for propagation of a carry signal. After all stages of addition, however, a conventional adder (such as the ripple-carry or the lookahead) must be used to combine the final sum and carry results.

3:2 compressors

A full adder can be viewed as a 3:2 lossy compressor: it sums three one-bit inputs and returns the result as a single two-bit number; that is, it maps 8 input values to 4 output values. (the term "compressor" instead of "counter" was introduced in[13])Thus, for example, a binary input of 101 results in an output of 1 + 0 + 1 = 10 (decimal number 2). The carry-out represents bit one of the result, while the sum represents bit zero. Likewise, a half adder can be used as a 2:2 lossy compressor, compressing four possible inputs into three possible outputs.

Such compressors can be used to speed up the summation of three or more addends. If the number of addends is exactly three, the layout is known as the carry-save adder. If the number of addends is four or more, more than one layer of compressors is necessary, and there are various possible designs for the circuit: the most common are Dadda and Wallace trees. This kind of circuit is most notably used in multiplier circuits, which is why these circuits are also known as Dadda and Wallace multipliers.

Quantum adders

Using only the Toffoli and CNOT quantum logic gates, it is possible to produce quantum full- and half-adders.[14][15][16] The same circuits can also be implemented in classical reversible computation, as both CNOT and Toffoli are also classical logic gates.

Since the quantum Fourier transform has a low circuit complexity, it can efficiently be used for adding numbers as well.[17][18][19]

Analog adders

Just as in Binary adders, combining two input currents effectively adds those currents together. Within the constraints of the hardware, non-binary signals (i.e. with a base higher than 2) can be added together to calculate a sum. Also known as a "summing amplifier",[20] this technique can be used to reduce the number of transistors in an addition circuit.

See also

- Binary multiplier

- Subtractor

- Electronic mixer — for adding analog signals

References

Further reading

External links

Wikiwand in your browser!

Seamless Wikipedia browsing. On steroids.

Every time you click a link to Wikipedia, Wiktionary or Wikiquote in your browser's search results, it will show the modern Wikiwand interface.

Wikiwand extension is a five stars, simple, with minimum permission required to keep your browsing private, safe and transparent.