TSMC to go 3D with wafer-sized processors — CoW-SoW technology allows 3D stacking for the world's largest chips

台積電將採用晶圓級處理器進行 3D 技術 — CoW-SoW 技術可實現全球最大晶片的 3D 堆疊

Massive wafer scale 'chips' to become even more formidable.

大規模晶圓級「晶片」變得更強大。

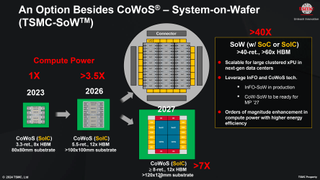

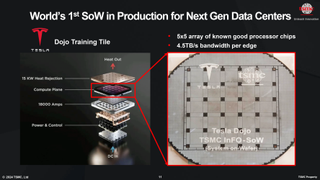

TSMC is taking the wafer-scale fabrication battle into the third dimension with a new technology. At its North American Technology Symposium, the company introduced its next-generation system-on-wafer platform—CoW-SoW—that will enable 3D integration with wafer-scale designs. This builds on the InFO_SoW system-on-wafer integration technology technology that TSMC introduced in 2020, which lets it build wafer-scale logic processors. So far, only Tesla has adopted this tech for its Dojo supercomputer, which TSMC says is now in production.

台積電正在利用新技術將晶圓級製造之戰帶入三維。在北美技術研討會上,該公司推出了下一代晶圓系統平台 CoW-SoW,該平台將實現與晶圓級設計的 3D 整合。該技術建立在台積電 2020 年推出的 InFO_SoW 晶圓級系統整合技術的基礎上,使其能夠建構晶圓級邏輯處理器。到目前為止,只有特斯拉在其 Dojo 超級電腦中採用了這項技術,台積電錶示該電腦現已投入生產。

In its forthcoming CoW-SoW platform, TSMC will merge two of its packaging methods — InFO_SoW and System on Integrated Chips (SoIC) — into its system-on-wafer platform. Using the Chip-on-Wafer (CoW) tech will enable the stacking of memory or logic directly atop a system-on-wafer. The new CoW_SoW technology is expected to be ready for large-scale production by 2027, though it remains to be seen when actual products arrive on the market.

在即將推出的 CoW-SoW 平台中,台積電將把兩種封裝方法——InFO_SoW 和整合式晶片系統 (SoIC)——合併到其晶圓系統平台中。使用晶圓晶片 (CoW) 技術將能夠將記憶體或邏輯直接堆疊在晶圓系統之上。新的CoW_SoW技術預計將在2027年實現大規模生產,但實際產品何時上市仍有待觀察。

"In the future, using wafer-level integrations [will allow] our customers to integrate even more logic and memory together," said Kevin Zhang, Vice President of Business Development at TSMC. "SoW is no longer a fiction; this is something we already work with our customers [on] to produce some of the products already in place. We think by leveraging our advanced wafer-level integration technology, we can provide our customer a very important path that allows them to continue to grow their capability to bring in more computation, more energy efficient computation, to their AI cluster or [supercomputer]."

「未來,使用晶圓級整合[將允許]我們的客戶將更多的邏輯和記憶體整合在一起,」台積電業務開發副總裁 Kevin 張表示。 「SoW 不再是虛構的;我們已經與客戶合作生產一些已經到位的產品。我們認為,透過利用我們先進的晶圓級整合技術,我們可以為客戶提供非常重要的產品使他們能夠繼續增強能力,為他們的人工智慧叢集或[超級電腦]引入更多計算、更節能的計算。

Currently, TSMC's CoW-SoW focuses on integrating wafer-scale processors with HBM4 memory. These next-generation memory stacks will feature a 2048-bit interface, which will make it feasible to integrate HBM4 directly on top of logic chips. Meanwhile, it may also make sense to stack additional logic on wafer-scale processors to optimize costs.

目前,台積電的CoW-SoW專注於將晶圓級處理器與HBM4記憶體整合。這些下一代記憶體堆疊將採用 2048 位元接口,這使得將 HBM4 直接整合在邏輯晶片頂部成為可能。同時,在晶圓級處理器上堆疊額外的邏輯以優化成本也可能是有意義的。

Wafer-scale processors in general (i.e., Cerebras's WSE), and InFO_SoW-based processors in particular, offer significant performance and efficiency benefits, including high-bandwidth and low-latency core-to-core communications, low power delivery network impedance, and high energy efficiency. As an added bonus, such processors also have additional redundancy in the form of 'extra' cores.

一般而言,晶圓級處理器(即Cerebras 的WSE),特別是基於InFO_SoW 的處理器,可提供顯著的性能和效率優勢,包括高頻寬和低延遲的核心到核心通訊、低功率傳輸網絡阻抗以及高能源效率。作為額外的好處,此類處理器還具有「額外」核心形式的額外冗餘。

However, the InFO_SoW technology has certain limitations. For instance, wafer-scale processors made using this method rely entirely on on-chip memory, which may fall short for future AI needs (but is good for now). CoW-SoW will solve this, as it will allow putting HBM4 on such wafers. In addition, InFO_SoW wafers are processed using a single node, and this node does not support 3D stacking, which will be supported by CoW-SoW products.

然而,InFO_SoW技術有一定的限制。例如,使用這種方法製造的晶圓級處理器完全依賴片上記憶體,這可能無法滿足未來人工智慧的需求(但目前來說很好)。 CoW-SoW 將解決這個問題,因為它將允許將 HBM4 放置在此類晶圓上。此外,InFO_SoW晶圓採用單節點加工,該節點不支援3D堆疊,而CoW-SoW產品將支援3D堆疊。

Stay on the Cutting Edge

保持領先地位

Join the experts who read Tom's Hardware for the inside track on enthusiast PC tech news — and have for over 25 years. We'll send breaking news and in-depth reviews of CPUs, GPUs, AI, maker hardware and more straight to your inbox.

與專家一起閱讀《Tom's Hardware》,了解發燒友 PC 技術新聞的內幕消息 — 閱讀時間已超過 25 年。我們會將有關 CPU、GPU、AI、創客硬體等的突發新聞和深入評論直接發送到您的收件匣。

Anton Shilov is a Freelance News Writer at Tom’s Hardware US. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

Anton Shilov 是 Tom’s Hardware US 的自由新聞撰稿人。在過去的幾十年裡,他涵蓋了從 CPU 和 GPU 到超級計算機,從現代工藝技術和最新的晶圓廠工具到高科技行業趨勢的一切。

論壇評論

-

edzieba 埃傑巴 A 'chip' sucking down 18,000 amps and shunting out 15kW. That'll need what, maybe 2 or 3 Noctua coolers?Reply 回覆

一個「晶片」吸收 18,000 安培電流並分流 15 千瓦。那需要什麼,也許 2 或 3 個 Noctua 冷卻器? -

HaninTH 哈寧TH Immersion cooling will be necessary for these massive things? Possibly with an exotic coolant.Reply 回覆

對於這些巨大的東西來說,浸沒式冷卻是必要的嗎?可能帶有異國情調的冷卻劑。 -

Notton 諾頓 How would you design a heatsink so it applies even pressure over that die size?Reply 回覆

您將如何設計散熱器,使其在該晶片尺寸上施加均勻的壓力?

How do you keep the die or joints from cracking when it goes through a heating/expansion and cooling/contraction cycle?

當模具或接頭經歷加熱/膨脹和冷卻/收縮循環時,如何防止模具或接頭破裂? -

Steve Nord_ 史蒂夫諾德_ Just regular microjet coolers would be lovely, but you guys are showing like legal size Culver's ads in a letter sized ad space, and it's trashing your columns. I'm not even getting swole from all the dairy, c'mon.Reply 回覆

普通的微噴射冷卻器就很不錯了,但是你們在信紙大小的廣告空間中展示了合法尺寸的卡爾弗廣告,這會破壞您的專欄。我甚至沒有因所有乳製品而感到臃腫,來吧。 -

Mpablo87 I heard some Austrian Startup offers ideas for cooling ! ! ! ! !Reply

Maybe that size is acceptable ? ! ? ! ?

Most Popular 最受歡迎

華為推出另一款由受認可的中國晶圓廠中芯國際製造的 7 奈米處理器—麒麟 9010 基於先前的設計

台積電將製造兩倍於當今最大晶片尺寸的大型晶片——晶片將使用數千瓦的功率

頂級半導體公司因美國制裁和激烈競爭而離開中國

中國開發了自己的Neuralink-Neucyber腦部介面來自一家神經技術公司