After I published my $1 MCU write-up, several readers suggested I look at application processors — the MMU-endowed chips necessary to run real operating systems like Linux.

在我发布了我的 1 美元微控制器书写之后,几位读者建议我关注应用处理器——那些必要的 MMU 加持芯片,以运行像 Linux 这样的真实操作系统。💻

Massive shifts over the last few years have seen internet-connected devices become more featureful (and hopefully, more secure), and I’m finding myself putting Linux into more and more places.

过去几年中,大规模的变化使得互联网连接的设备变得功能更加丰富(并且希望更加安全),我发现自己将 Linux 应用于越来越多的地方。📱

Among beginner engineers, application processors supplicate reverence: one minor PCB bug and your $10,000 prototype becomes a paperweight.

在初学工程师中,应用处理器备受敬畏:一个小小的 PCB 故障,你的$10,000 原型就会变成一个废纸镇 😟。

There’s an occult consortium of engineering pros who drop these chips into designs with utter confidence, while the uninitiated cower for their Raspberry Pis and overpriced industrial SOMs.

有一个神秘的工程师联盟,他们自信地将这些芯片融入设计中,而外行人却为他们的树莓派和价格过高的工业 SOM 感到畏惧。🛠️

This article is targeted at embedded engineers who are familiar with microcontrollers but not with microprocessors or Linux, so I wanted to put together something with a quick primer on why you’d want to run embedded Linux, a broad overview of what’s involved in designing around application processors, and then a dive into some specific parts you should check out — and others you should avoid — for entry-level embedded Linux systems.

这篇文章是针对那些熟悉微控制器但对微处理器或 Linux 不太了解的嵌入式工程师,因此我想整理一些内容,以快速介绍为什么你会想要运行嵌入式 Linux,概述一下设计应用处理器时需要涉及的内容,然后深入探讨一些你应该关注的特定部分——以及一些你应该避免的部分——以便于入门级嵌入式 Linux 系统。🌟

Just like my microcontroller article, the parts I picked range from the well-worn horses that have pulled along products for the better part of this decade, to fresh-faced ICs with intriguing capabilities that you can keep up your sleeve.

就像我的微控制器文章一样,我挑选的部件涵盖了从这一整个十年中一直在推动产品发展的老将,到那些具有令人着迷能力的新面孔集成电路,可以随着你的需要灵活运用。🔧

If my mantra for the microcontroller article was that you should pick the right part for the job and not be afraid to learn new software ecosystems, my argument for this post is even simpler: once you’re booted into Linux on basically any of these parts, they become identical development environments.

如果我在微控制器文章中的座右铭是你应该选择合适的零件来完成工作,并且不要害怕学习新的软件生态系统,那么我对这篇帖子论点就更简单了:一旦你在这些零件上的 Linux 系统启动,你会发现它们变成了相同的开发环境。💻

That makes chips running embedded Linux almost a commodity product: as long as your processor checks off the right boxes, your application code won’t know if it’s running on an ST or a Microchip part — even if one of those is a brand-new dual-core Cortex-A7 and the other is an old ARM9.

这使得运行嵌入式 Linux 的芯片几乎成为一种商品产品:只要你的处理器符合正确的标准,您的应用代码就不会知道它是运行在 ST 还是 Microchip 的产品上——即使其中一个是全新的双核 Cortex-A7,而另一个是旧的 ARM9。💻

Your I2C drivers, your GPIO calls — even your V4L-based image processing code — will all work seamlessly.

您的 I2C 驱动程序、GPIO 调用——甚至基于 V4L 的图像处理代码——都将无缝工作。 😊

At least, that’s the sales pitch. Getting a part booted is an entirely different ordeal altogether — that’s what we’ll be focused on. Except for some minor benchmarking at the end, once we get to a shell prompt, we’ll consider the job completed.

至少,这就是销售宣传。启动一个部件完全是另一回事——这就是我们将要关注的内容。除了最后的几项小基准测试,一旦我们进入命令行提示符,我们将认为任务已经完成。💻

As a departure from my microcontroller review, this time I’m focusing heavily on hardware design: unlike the microcontrollers I reviewed, these chips vary considerably in PCB design difficulty — a discussion I would be in error to omit.

此次我将重点关注硬件设计,作为我微控制器评测的一个转变:与我评测的微控制器不同,这些芯片在 PCB 设计的难度上差异较大——这是我在讨论中不应遗漏的内容。🔧

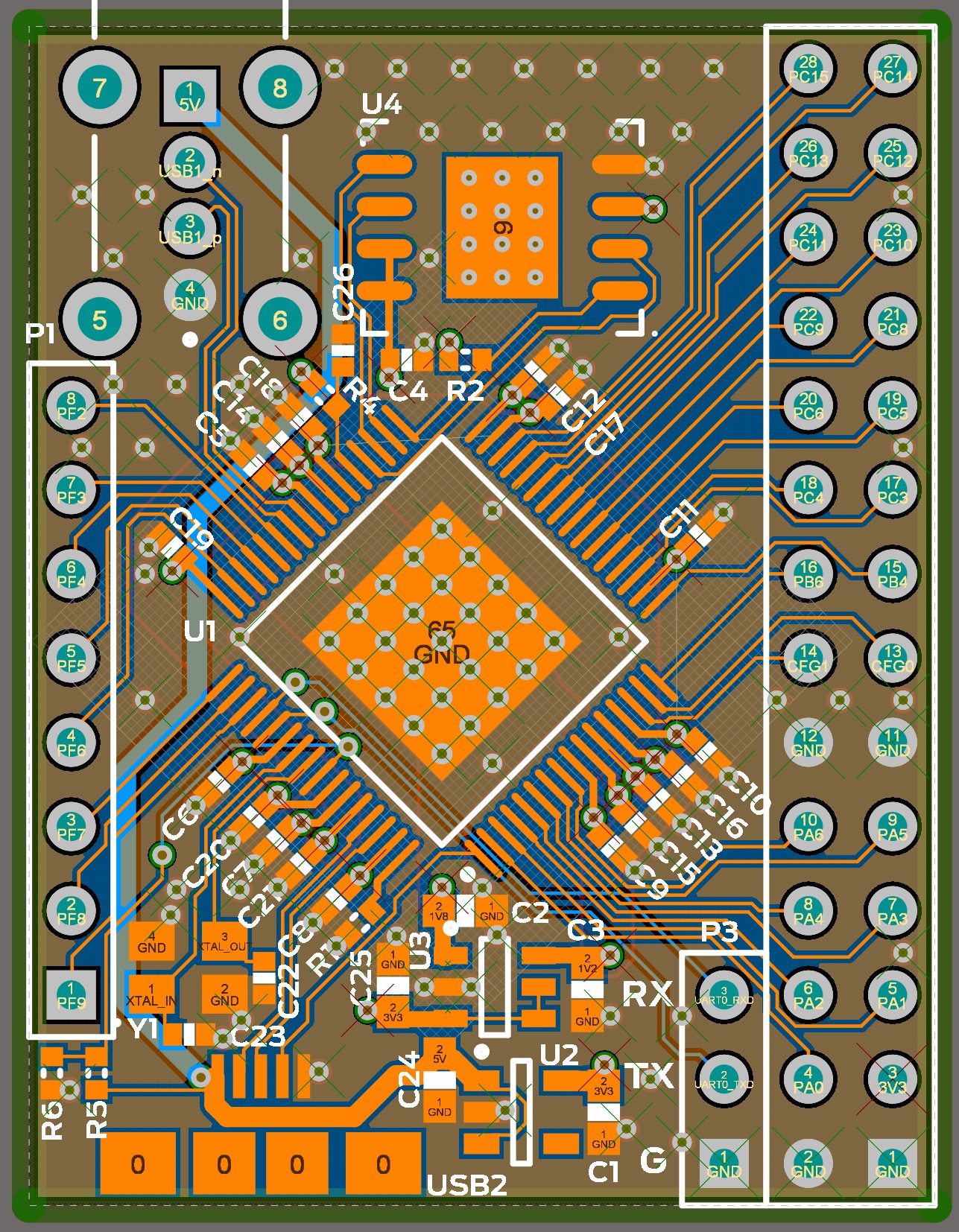

To this end, I designed a dev board from scratch for each application processor reviewed. Well, actually, many dev boards for each processor: roughly 25 different designs in total. This allowed me to try out different DDR layout and power management strategies — as well as fix some bugs along the way.

为此,我为每个审查过

I intentionally designed these boards from scratch rather than starting with someone else’s CAD files. This helped me discover little “gotchas” that each CPU has, as well as optimize the design for cost and hand-assembly.

我故意从零开始设计这些电路板,而不是使用其他人的 CAD 文件。💻 这帮助我发现了每个 CPU 的小“陷阱”,并优化了成本和手工组装设计。💡

Each of these boards was designed across one or two days’ worth of time and used JLC’s low-cost 4-layer PCB manufacturing service.

每块电路板的设计耗时一到两天,并使用了 JLC 的低成本 4 层 PCB 制造服务。🛠️

These boards won’t win any awards for power consumption or EMC: to keep things easy, I often cheated by combining power rails together that would typically be powered (and sequenced!) separately.

这些电路板在功耗或电磁兼容性方面不会获得任何奖项:为了让事情更简单,我经常通过将通常需要单独供电(并且需要按顺序供电!)的电源轨合并在一起来作弊。⚡️

Also, I limited the on-board peripherals to the bare minimum required to boot, so there are no audio CODECs, little I2C sensors, or Ethernet PHYs on these boards.

此外,我将板载外围设备限制到引导所需的最低限度,因此这些板上没有音频编码解码器、很少的 I2C 传感器或以太网物理层接口。📉

As a result, the boards I built for this review are akin to the notes from your high school history class or a recording you made of yourself practicing a piece of music to study later.

因此,我为这次评测制作的电路板就像你高中历史课的笔记,或者你为以后复习而录的自己练习音乐的录音。📚

So while I’ll post pictures of the boards and screenshots of layouts to illustrate specific points, these aren’t intended to serve as reference designs or anything; the whole point of the review is to get you to a spot where you’ll want to go off and design your own little Linux boards. Teach a person to fish, you know?

所以虽然我会发布一些电路板的图片和布局的截图以说明特定的观点,但这些并不打算作为参考设计或其他什么;这次评测的整个目的就是让你达到一个你想自己设计小型 Linux 电路板的地方。教人钓鱼,你懂的?🐟

Microcontroller vs Microprocessor: Differences

微控制器与微处理器:区别 🔍

Coming from microcontrollers, the first thing you’ll notice is that Linux doesn’t usually run on Cortex-M, 8051, AVR, or other popular microcontroller architectures. Instead, we use application processors — popular ones are the Arm Cortex-A, ARM926EJ-S, and several MIPS iterations.

来自于微控制器,你会首先注意到 Linux 通常不运行在 Cortex-M、8051、AVR 或其他流行的微控制器架构上。🔍相反,我们使用应用处理器——流行的有 Arm Cortex-A、ARM926EJ-S 和几个 MIPS 变种。📱

The biggest difference between these application processors and a microcontroller is quite simple: microprocessors have a memory management unit (MMU), and microcontrollers don’t. Yes, you can run Linux without an MMU, but you usually shouldn’t: Cortex-M7 parts that can barely hit 500 MHz routinely go for double or quadruple the price of faster Cortex-A7s. They’re power-hungry: microcontrollers are built on larger processes than application processors to reduce their leakage current.

这些应用处理器和微控制器之间最大的区别非常简单:微处理器拥有内存管理单元(MMU),而微控制器没有。💡 是的,你可以在没有 MMU 的情况下运行 Linux,但通常不应该:那些几乎只能达到 500 MHz 的 Cortex-M7 部件,价格往往是更快的 Cortex-A7 的两倍或四倍。💰 它们耗电较大:微控制器的制造工艺比应用处理器更大,以减少漏电流。⚡️

And without an MMU and generally-low clock speeds, they’re downright slow.

没有内存管理单元(MMU)和通常较低的时钟速度,它们的速度确实很慢。🐢

Other than the MMU, the lines between MCUs and MPUs are getting blurred. Modern application processors often feature a similar peripheral complement as microcontrollers, and high-end Cortex-M7 microcontrollers often have similar clock speeds as entry-level application processors.

除了内存管理单元(MMU)之外,微控制器(MCU)和微处理器(MPU)之间的界限越来越模糊。现代应用处理器通常具有与微控制器相似的外设配置,而高端 Cortex-M7 微控制器的时钟速度通常与入门级应用处理器相似。🔗

Why would you want to Linux?

为什么你想使用 Linux 呢?🐧

When your microcontroller project outgrows its super loop and the random ISRs you’ve sprinkled throughout your code with care, there are many bare-metal tasking kernels to turn to — FreeRTOS, ThreadX (now Azure RTOS), RT-Thread, μC/OS, etc. By an academic definition, these are operating systems. However, compared to Linux, it’s more useful to think of these as a framework you use to write your bare-metal application inside.

当你的微控制器项目超出了超级循环以及你在代码中精心植入的随机中断服务例程的范围时,有许多裸机任务内核可供选择——FreeRTOS、ThreadX(现在称为 Azure RTOS)、RT-Thread、μC/OS 等。从学术的定义来看,这些都是操作系统。然而,与 Linux 相比,将这些视为一个框架,用于在其中编写你的裸机应用程序,会更有用。🛠️

They provide the core components of an operating system: threads (and obviously a scheduler), semaphores, message-passing, and events. Some of these also have networking, filesystems, and other libraries.

它们提供了操作系统的核心组件:线程(显然还有一个调度程序)、信号量、消息传递和事件。某些组件还包括网络功能、文件系统和其他库。🖥️

Comparing bare-metal RTOSs to Linux simply comes down to the fundamental difference between these and Linux: memory management and protection.

将裸机实时操作系统(RTOS)与 Linux 进行比较,归根结底是这两者与 Linux 之间的根本区别:内存管理和保护。🛡️

This one technical difference makes Linux running on an application processor behave quite differently from your microcontroller running an RTOS.((Before the RTOS snobs attack with pitchforks, yes, there are large-scale, well-tested RTOSes that are usually run on application processors with memory management units.

这个技术差异使得运行在应用处理器上的 Linux 与运行在实时操作系统(RTOS)上的微控制器表现得截然不同。🔧(在 RTOS 爱好者来攻击之前,是的,确实有大规模且经过充分测试的 RTOS,通常运行在带有内存管理单元的应用处理器上。)📊

Look at RTEMS as an example. They don’t have some of the limitations discussed below, and have many advantages over Linux for safety-critical real-time applications.))

将 RTEMS 作为一个例子。它们没有下面讨论的一些限制,并且在安全关键型实时应用中比 Linux 有许多优势。🚀

Dynamic memory allocation

动态内存分配🛠️

Small microcontroller applications can usually get by with static allocations for everything, but as your application grows, you’ll find yourself calling malloc() more and more, and that’s when weird bugs will start creeping up in your application.

小型微控制器应用通常可以用静态分配来解决所有问题,但随着应用程序的增长,你会发现自己越来越多地调用 malloc(),这时奇怪的错误将开始在你的应用中出现。🛠️

With complex, long-running systems, you’ll notice things working 95% of the time — only to crash at random (and usually inopportune) times.

在复杂且长期运行的系统中,你会发现其工作正常的概率为 95%——但却会在随机(通常不合时宜)的时刻崩溃。💻

These bugs evade the most javertian developers, and in my experience, they almost always stem from memory allocation issues: usually either memory leaks (that can be fixed with appropriate free() calls), or more serious problems like memory fragmentation (when the allocator runs out of appropriately-sized free blocks).

这些错误使得最严格的开发者都无法发现,根据我的经验,它们几乎总是源于内存分配问题:通常要么是内存泄漏(可以通过适当的 free() 调用来修复),要么是更严重的问题,如内存碎片(当分配器耗尽了合适大小的空闲块时)。🛠️

Because Linux-capable application processors have a memory management unit, *alloc() calls execute swiftly and reliably. Physical memory is only reserved (faulted in) when you actually access a memory location. Memory fragmentation is much less an issue since Linux frees and reorganizes pages behind the scenes. Plus, switching to Linux provides easier-to-use diagnostic tools (like valgrind) to catch bugs in your application code in the first place. And finally, because applications run in virtual memory, if your app does have memory bugs in it, Linux will kill it — leaving the rest of your system running. ((As a last-ditch kludge, it’s not uncommon to call your app in a superloop shell script to automatically restart it if it crashes without having to restart the entire system.))

因为支持 Linux 的应用处理器具有内存管理单元,因此*alloc()调用执行得迅速而可靠。💻 物理内存仅在您实际访问某个内存位置时才会被保留(发生故障)。🛠️ 由于 Linux 在后台释放和重组页面,内存碎片化问题大大减少。📉 而且,切换到 Linux 提供了更易于使用的诊断工具(如 valgrind),从而能更早地发现应用代码中的 BUG。🐞最后,由于应用程序在虚拟内存中运行,如果您的应用程序确实存在内存 BUG,Linux 将会终止它——使您的系统其他部分继续运行。⚙️(作为一个最后的应急措施,通常会在超级循环 shell 脚本中调用您的应用程序,以便在崩溃时自动重启,而不需要重启整个系统。)🔄

Networking & Interoperability

网络与互操作性 🌐

Running something like lwIP under FreeRTOS on a bare-metal microcontroller is acceptable for a lot of simple applications, but application-level network services like HTTP can burden you to implement in a reliable fashion.

在裸机微控制器上,使用 FreeRTOS 运行像 lwIP 这样的东西对许多简单应用来说是可以接受的,但应用层网络服务如 HTTP 可能会使您在实现可靠性时感到压力。🌐

Stuff that seems simple to a desktop programmer — like a WebSockets server that can accept multiple simultaneous connections — can be tricky to implement in bare-metal network stacks.

对桌面程序员来说似乎很简单的事情,比如一个可以接受多个同时连接的 WebSockets 服务器,在裸机网络堆栈中实现起来可能会很棘手。💻

Because C doesn’t have good programming constructs for asynchronous calls or exceptions, code tends to contain either a lot of weird state machines or tons of nested branches. It’s horrible to debug problems that occur.

由于 C 语言对异步调用或异常处理没有良好的编程结构,代码往往包含大量奇怪的状态机或成吨的嵌套分支。调试出现的问题非常困难。😩

In Linux, you get a first-class network stack, plus tons of rock-solid userspace libraries that sit on top of that stack and provide application-level network connectivity.

在 Linux 中,您可以获得一流的网络栈,以及许多可靠的用户空间库,这些库位于该网络栈之上,提供应用级的网络连接。🌐

Plus, you can use a variety of high-level programming languages that are easier to handle the asynchronous nature of networking.

另外,您可以使用多种高层次的编程语言,这些语言更容易处理网络的异步特性。💻

Somewhat related is the rest of the standards-based communication / interface frameworks built into the kernel. I2S, parallel camera interfaces, RGB LCDs, SDIO, and basically all those other scary high-bandwidth interfaces seem to come together much faster when you’re in Linux.

与内核中内置的其他基于标准的通信/接口框架有些相关。🔗 I2S、并行摄像头接口、RGB LCD、SDIO 以及基本上所有其他那些令人畏惧的高带宽接口,当你在 Linux 中时似乎能更快地整合在一起。🚀

But the big one is USB host capabilities. On Linux, USB devices just work. If your touchscreen drivers are glitching out and you have a client demo to show off in a half-hour, just plug in a USB mouse until you can fix it (I’ve been there before). Product requirements change and now you need audio?

但最重要的是 USB 主机功能。在 Linux 系统中,USB 设备可以轻松使用。如果你的触摸屏驱动出现故障,而你还有半小时的客户演示要展示,只需插入一个 USB 鼠标,直到你能解决这个问题(我经历过这样的情况)。产品需求会改变,现在你需要音频功能了吗?🖥️

Grab a $20 USB dongle until you can respin the board with a proper audio codec. On many boards without Ethernet, I just use a USB-to-Ethernet adapter to allow remote file transfer and GDB debugging.

抓一个 20 美元的 USB 加密狗,直到你能够重新设计电路板,使用合适的音频编码器。🌐 在许多没有以太网的电路板上,我只是使用 USB 转以太网适配器来进行远程文件传输和 GDB 调试。🔌

Don’t forget that, at the end of the day, an embedded Linux system is shockingly similar to your computer.

别忘了,归根结底,嵌入式 Linux 系统与你的电脑惊人地相似。💻

Security 安全 🔒

When thinking about embedded device security, there are usually two things we’re talking about: device security (making sure the device can only boot from verified firmware), and network security (authentication, intrusion prevention, data integrity checks, etc).

在考虑嵌入式设备安全时,我们通常谈论两个方面:设备安全(确保设备只能从经过验证的固件启动)🔐,以及网络安全(身份验证、入侵防御、数据完整性检查等)🌐。

Device security is all about chain of trust: we need a bootloader to read in an encrypted image, decrypt and verify it, before finally executing it. The bootloader and keys need to be in ROM so that they cannot be modified.

设备安全完全依赖于信任链:我们需要一个引导加载程序来读取加密的映像,解密并验证它,然后最终执行它。引导加载程序和密钥需要存储在只读存储器中,以防止它们被修改。🔐

Because the image is encrypted, nefarious third-parties won’t be able to install the firmware on cloned hardware. And since the ROM authenticates the image before executing, people won’t be able to run custom firmware on the hardware.

因为图像是加密的,恶意的第三方将无法在克隆硬件上安装固件。🔒 而且由于 ROM 在执行之前会验证图像,人们无法在硬件上运行自定义固件。🚫

Network security is about limiting software vulnerabilities and creating a trusted execution environment (TEE) where cryptographic operations can safely take place. The classic example is using client certificates to authenticate our client device to a server.

网络安全是限制软件漏洞并创建一个可信执行环境(TEE),在这个环境中,可以安全地进行加密操作。🔐 经典的例子是使用客户端证书来验证我们的客户端设备与服务器的身份。🔒

If we perform the cryptographic hashing operation in a secure environment, even an attacker who has gained total control over our normal execution environment would be unable to read our private key.

如果我们在安全环境中执行加密哈希操作,即使攻击者完全控制了我们的正常执行环境,也无法读取我们的私钥。🔒

In the world of microcontrollers, unless you’re using one of the newer Cortex-M23/M33 cores, your chip probably has a mishmash of security features that include hardware cryptographic support, (notoriously insecure) flash read-out protection, execute-only memory, write protection, TRNG, and maybe a memory protection unit.

在微控制器的世界中,除非你使用的是较新的 Cortex-M23/M33 核心,否则你的芯片可能混合了多种安全特性,包括硬件加密支持、(臭名昭著的不安全)闪存读取保护、只读内存、写保护、真随机数生成器(TRNG),以及可能的内存保护单元。🔒

While vendors might have an app note or simple example, it’s usually up to you to get all of these features enabled and working properly, and it’s challenging to establish a good chain of trust, and nearly impossible to perform cryptographic operations in a context that’s not accessible by the rest of the system.

尽管供应商可能提供应用说明或简单的示例,但通常还是需要你自己来使所有这些功能启用并正常工作,而建立良好的信任链是很具挑战性的,在不让系统其他部分访问的上下文中几乎不可能进行加密操作。🛠️

Secure boot isn’t available on every application processor reviewed here, it’s much more common.

安全启动并不是所有这里评测的应用处理器都有,但它更为常见。🔐

While there are still vulnerabilities that get disclosed from time to time, my non-expert opinion is that the implementations seem much more robust than on Cortex-M parts: boot configuration data and keys are stored in one-time-programmable memory that is not accessible from non-privileged code.

虽然仍然不时有漏洞被披露,但我作为非专家的看法是,实施似乎比 Cortex-M 部件更为稳健:启动配置数据和密钥存储在一次性可编程内存中,无法从非特权代码访问。🔒

Network security is also more mature and easier to implement using Linux network stack and cryptography support, and OP-TEE provides a ready-to-roll secure environment for many parts reviewed here.

网络安全也更加成熟,并且在使用 Linux 网络栈和加密支持方面更易于实施,OP-TEE 为这里审查的许多部分提供了一个现成的安全环境。🔒

Filesystems & Databases 文件系统与数据库 📁📊

Imagine that you needed to persist some configuration data across reboot cycles. Sure, you can use structs and low-level flash programming code, but if this data needs to be appended to or changed in an arbitrary fashion, your code would start to get ridiculous.

想象一下,你需要在重启周期中保持一些配置数据。🖥️ 当然,你可以使用结构体和低级的闪存编程代码,但如果这些数据需要以任意方式追加或更改,你的代码就会变得复杂且难以维护。😅

That’s why filesystems (and databases) exist. Yes, there are embedded libraries for filesystems, but these are way clunkier and more fragile than the capabilities you can get in Linux with nothing other than ticking a box in menuconfig. And databases?

这就是文件系统(和数据库)存在的原因。📁 是的,确实有嵌入式库用于文件系统,但这些库比在 Linux 中仅需在 menuconfig 中勾选一个选项所能获得的功能要笨重得多且更脆弱。💻 那数据库呢?📊

I’m not sure I’ve ever seen an honest attempt to run one on a microcontroller, while there’s a limitless number available on Linux.

我不确定我是否见过在微控制器上运行它的诚实尝试,而在 Linux 上则有无数可用的选项。🤖

Multiple Processes 多个进程 🌀

In a bare-metal environment, you are limited to a single application image. As you build out the application, you’ll notice things get kind of clunky if your system has to do a few totally different things simultaneously.

在裸机环境中,您仅限于一个应用程序镜像。🖥️ 随着您构建应用程序,您会注意到,如果系统必须同时执行几项完全不同的任务,情况会变得有些笨重。⚙️

If you’re developing for Linux, you can break this functionality into separate processes, where you can develop, debug, and deploy separately as separate binary images.

如果您正在为 Linux 开发,可以将此功能拆分为不同的进程,您可以分开开发、调试和部署,作为独立的二进制映像。💻

The classic example is the separation between the main app and the updater. Here, the main app runs your device’s primary functionality, while a separate background service can run every day to phone home and grab the latest version of the main application binary.

经典例子是主应用和更新程序之间的分离。📱在这里,主应用运行设备的主要功能,而一个独立的后台服务可以每天运行,联系主服务器获取主应用的最新版本。🔄

These apps do not have to interact at all, and they perform completely different tasks, so it makes sense to split them up into separate processes.

这些应用程序不需要相互互动,并且它们执行的任务完全不同,因此将它们分成单独的进程是合理的。💻

Language and Library Support

语言和库支持 📚

Bare-metal MCU development is primarily done in C and C++. Yes, there are interesting projects to run Python, Javascript, C#/.NET, and other languages on bare metal, but they’re usually focused on implementing the core language only; they don’t provide a runtime that is the same as a PC. And even their language implementation is often incompatible. That means your code (and the libraries you use) have to be written specifically for these micro-implementations. As a result, just because you can run MicroPython on an ESP32 doesn’t mean you can drop Flask on it and build up a web application server. By switching to embedded Linux, you can use the same programming languages and software libraries you’d use on your PC.

裸机微控制器开发主要使用 C 和 C++进行。💻 是的,确实有一些有趣的项目可以在裸机上运行 Python、Javascript、C#/.NET 和其他语言,但它们通常仅专注于实现核心语言;它们并不提供与 PC 相同的运行时环境。🔍 即使它们的语言实现通常也不兼容。⚠️ 这意味着你编写的代码(以及你使用的库)必须专门为这些微型实现编写。✍️ 因此,仅仅因为你可以在 ESP32 上运行 MicroPython,并不意味着你可以在上面运行 Flask 并构建一个 Web 应用服务器。🌐 通过切换到嵌入式 Linux,你可以使用与在 PC 上相同的编程语言和软件库。📦

Brick-wall isolation from the hardware

硬件的砖墙隔离 🧱

Classic bare-metal systems don’t impose any sort of application separation from the hardware. You can throw a random I2C_SendReceive() function in anywhere you’d like.

经典的裸机系统并不对硬件和应用程序之间进行任何形式的分离。您可以随意在任何地方放置一个随机的 I2C_SendReceive() 函数。🎉

In Linux, there is a hard separation between userspace calls and the underlying hardware driver code.

在 Linux 中,用户空间调用与底层硬件驱动代码之间有严格的分离。🔧

One key advantage of this is how easy it is to move from one hardware platform to another; it’s not uncommon to only have to change a couple of lines of code to specify the new device names when porting your code.

这一点的一个主要优点是从一个硬件平台迁移到另一个平台是多么简单;在移植代码时,只需更改几行代码来指定新设备名称的情况并不少见。🚀

Yes, you can poke GPIO pins, perform I2C transactions, and fire off SPI messages from userspace in Linux, and there are some good reasons to use these tools during diagnosing and debugging.

是的,您可以在 Linux 中从用户空间操作 GPIO 引脚、执行 I2C 交易并发送 SPI 消息,而且在诊断和调试过程中使用这些工具有一些很好的理由。🔧

Plus, if you’re implementing a custom I2C peripheral device on a microcontroller, and there’s very little configuration to be done, it may seem silly to write a kernel driver whose only job is to expose a character device that basically passes on whatever data directly to the I2C device you’ve built.

此外,如果您在微控制器上实现一个自定义的 I2C 外设设备,而配置工作非常有限,那么编写一个内核驱动程序的唯一工作是暴露一个字符设备,这个设备基本上就是直接将任何数据传递给您构建的 I2C 设备,这似乎显得有些愚蠢。😅

But if you’re interfacing with off-the-shelf displays, accelerometers, IMUs, light sensors, pressure sensors, temperature sensors, ADCs, DACs, and basically anything else you’d toss on an I2C or SPI bus, Linux already has built-in support for this hardware that you can flip on when building your kernel and configure in your DTS file.

但是如果你是在与现成的显示器、加速度计、IMU、光传感器、压力传感器、温度传感器、ADC、DAC,以及基本上任何你会挂在 I2C 或 SPI 总线上的设备进行接口,Linux 已经内置了对这些硬件的支持,你可以在构建内核时开启并在 DTS 文件中进行配置。🛠️

Developer Availability and Cost

开发者的可用性和成本 💼

When you combine all these challenges together, you can see that building out bare-metal C code is challenging (and thus expensive).

当你将所有这些挑战结合在一起时,你会发现构建裸机 C 代码是具有挑战性的(因此成本高昂)。💻

If you want to be able to staff your shop with lesser-experienced developers who come from web-programming code schools or otherwise have only basic computer science backgrounds, you’ll need an architecture that’s easier to develop on.

如果您想能将您的商店配备经验较少的开发人员,这些开发人员可能来自网页编程的编码学校或仅具备基本计算机科学背景,您将需要一个更易于开发的架构。🛠️

This is especially true when the majority of the project is hardware-agnostic application code, and only a minor part of the project is low-level hardware interfacing.

这尤其适用于大部分项目是与硬件无关的应用代码,而只有一小部分是低层次的硬件接口。⚙️

Why shouldn’t you Linux? 你为什么不应该使用 Linux 呢?🤔

There are lots of good reasons not to build your embedded system around Linux:

有很多好的理由不把你的嵌入式系统建立在 Linux 之上:🤔

Sleep-mode power consumption. First, the good news: active mode power consumption of application processors is quite good when compared to microcontrollers. These parts tend to be built on smaller process nodes, so you get more megahertz for your ampere than the larger processes used for Cortex-M devices.

睡眠模式下的功耗。首先,好消息是:与微控制器相比,应用处理器在工作模式下的功耗相当不错。 🔋 这些部件往往采用更小的工艺节点制造,因此在使用的每安培中,你可以获得比 Cortex-M 设备所用的较大工艺更多的兆赫兹。 ⚡️

Unfortunately, embedded Linux devices have a battery life that’s measured in hours or days, not months or years.

不幸的是,嵌入式 Linux 设备的电池寿命以小时或天来计算,而不是以月或年来计算。🔋

Modern low-power microcontrollers have a sleep-mode current consumption in the order of 1 μA — and that figure includes SRAM retention and usually even a low-power RTC oscillator running.

现代低功耗微控制器的睡眠模式电流消耗大约在 1 μA 左右——这个数字包括了 SRAM 保持,并且通常还包括一个低功耗的 RTC 振荡器运行。💡

Low-duty-cycle applications (like a sensor that logs a data point every hour) can run off a watch battery for a decade.

低占空比应用(比如每小时记录一个数据点的传感器)可以用手表电池持续运行十年。⌚

Application processors, however, can use 300 times as much power while asleep (that leaky 40 nm process has to catch up with us eventually!), but even that pales in comparison to the SDRAM, which can eat through 10 mA (yes mA, not μA) or more in self-refresh mode. Sure, you can suspend-to-flash (hibernate), but that’s only an option if you don’t need responsive wake-up.

应用处理器在休眠时的功耗可以高达 300 倍(那种漏电的 40 纳米工艺总有一天会追上我们!)⚡,但即便如此,与 SDRAM 相比仍显得微不足道,SDRAM 在自刷新模式下的功耗可以达到 10 毫安(没错,是毫安,不是微安)或更多。💡当然,你可以选择挂起到闪存(休眠),但这仅在你不需要快速唤醒的情况下才是一个选项。🌙

Even companies like Apple can’t get around these fundamental limitations: compare the 18-hour battery life of the Apple Watch (which uses an application processor) to the 10-day life of the Pebble (which uses an STM32 microcontroller with a battery half the size of the Apple Watch).

即使是像苹果这样的公司也无法克服这些基本限制:比较一下苹果手表的 18 小时电池续航(使用应用处理器)与 Pebble 的 10 天续航(使用尺寸只有苹果手表一半的 STM32 微控制器的电池)。⌚️

Boot time. Embedded Linux systems can take several seconds to boot up, which is orders of magnitude longer than a microcontroller’s start-up time.

启动时间。嵌入式 Linux 系统的启动时间可能需要几秒钟,这比微 controller 的启动时间长几个数量级。⏱️

Alright, to be fair, this is a bit of an apples-to-oranges comparison: if you were to start initializing tons of external peripherals, mount a filesystem, and initialize a large application in an RTOS on a microcontroller, it could take several seconds to boot up as well.

好吧,公平地说,这有点像苹果对橘子的比较:如果你开始初始化大量外部外设,挂载文件系统,并在微控制器上的实时操作系统中初始化一个大型应用程序,启动也可能需要几秒钟的时间。🍏🍊

While boot time is a culmination of tons of different components that can all be tweaked and tuned, the fundamental limit is caused by application processors’ inability to execute code from external flash memory; they must copy it into RAM first ((unless you’re running an XIP kernel)).

启动时间是许多不同组件调整和优化的结果,但根本限制源于应用处理器无法直接从外部闪存执行代码;它们必须先将代码复制到 RAM 中(除非你正在运行 XIP 内核)。⏱️

Responsiveness. By default, Linux’s scheduler and resource system are full of unbounded latencies that under weird and improbable scenarios may take a long time to resolve (or may actually never resolve). Have you ever seen your mouse lock up for 3 seconds randomly? There you go. If you’re building a ventilator with Linux, think carefully about that. To combat this, there’s been a PREEMPT_RT patch for some time that turns Linux into a real-time operating system with a scheduler that can basically preempt anything to make sure a hard-real-time task gets a chance to run.

响应性。默认情况下,Linux 的调度器和资源系统充满了不受限制的延迟,在奇怪且不太可能的情况下,可能需要很长时间才能解决(或者实际上可能永远无法解决)。你是否曾经看到过你的鼠标随机卡住 3 秒钟?就是这样。如果你正在用 Linux 构建一台呼吸机,请仔细考虑这一点。为了应对这一问题,已经有一段时间存在 PREEMPT_RT 补丁,将 Linux 转变为实时操作系统,其调度器基本上可以中断任何任务,以确保硬实时任务有机会运行。🕒

Also, when many people think they need a hard-real-time kernel, they really just want their code to be low-jitter.

此外,当许多人认为他们需要一个硬实时内核时,他们实际上只希望他们的代码具有低抖动。🌟

Coming from Microcontrollerland, it feels like a 1000 MHz processor should be able to bit-bang something like a 50 kHz square wave consistently, but you would be wrong.

来自微控制器的世界,感觉像是一个 1000 MHz 的处理器应该能够稳定地生成 50 kHz 的方波,但你会错的。⚙️

The Linux scheduler is going to give you something on the order of ±10 µs of jitter for interrupts, not the ±10 ns jitter you’re used to on microcontrollers.

Linux 调度程序将为中断提供大约 ±10 微秒的抖动,而不是您在微控制器上习惯的 ±10 纳秒的抖动。⌛

This can be remedied too, though: while Linux gobbles up all the normal ARM interrupt vectors, it doesn’t touch FIQ, so you can write custom FIQ handlers that execute completely outside of kernel space.

这也可以解决:虽然 Linux 会吞噬所有正常的 ARM 中断向量,但它不触及 FIQ,因此你可以编写自定义的 FIQ 处理程序,这些处理程序完全在内核空间之外执行。💻

Honestly, in practice, it’s much more common to just delegate these tasks to a separate microcontroller. Some of the parts reviewed here even include a built-in microcontroller co-processor designed for controls-oriented tasks, and it’s also pretty common to just solder down a $1 microcontroller and talk to it over SPI or I2C.

说实话,在实际应用中,将这些任务委托给一个独立的微控制器要普遍得多。🔧 这里评审的一些部件甚至包括一个内置的微控制器协处理器,旨在处理控制相关的任务,而且仅仅焊接一个 1 美元的微控制器,通过 SPI 或 I2C 与其通信也是相当常见的。💻

Design Workflow 设计工作流程🔄

The first step is to architect your system.

第一步是设计你的系统。🛠️

This is hard to do unless what you’re building is trivial or you have a lot of experience, so you’ll probably start by buying some reference hardware, trying it out to see if it can do what you’re trying to do (both in terms of hardware and software), and then using that as a jumping-off point for your own designs.

这很难做到,除非你正在构建的东西是微不足道的,或者你有丰富的经验,因此你可能会先购买一些参考硬件,尝试一下看看它是否能实现你想做的事情(无论是硬件还是软件),然后以此为基础开始你的设计。🔧

I want to note that many designers focus too heavily on the hardware peripheral selection of the reference platform when architecting their system, and don’t spend enough time thinking about software early on.

我想指出,许多设计师在构建系统时过于关注参考平台的硬件外设选择,而没有花足够的时间在早期思考软件。💻

Just because your 500 MHz Cortex-A5 supports a parallel camera sensor interface doesn’t mean you’ll be able to forward-prop images through your custom SegNet implementation at 30 fps, and many parts reviewed here with dual Ethernet MACs would struggle to run even a modest web app.

仅仅因为你的 500 MHz Cortex-A5 支持并行相机传感器接口,并不意味着你能够以 30 帧每秒的速度通过自定义的 SegNet 实现传输图像,许多这里评论的具备双以太网 MAC 的部件甚至难以运行一个适度的网页应用程序。📸

Figuring out system requirements for your software frameworks can be rather unintuitive. For example, doing a multi-touch-capable finger-painting app in Qt 5 is actually much less of a resource hog than running a simple backend server for a web app written in a modern stack using a JIT-compiled language.

为您的软件框架确定系统需求可能会相当不直观。🛠️ 例如,在 Qt 5 中开发一个支持多点触控的指绘应用实际上比运行一个简单的后端服务器(为使用 JIT 编译语言现代技术栈编写的 web 应用)消耗的资源要少得多。🌐

Many developers familiar with traditional Linux server/desktop development assume they’ll just throw a .NET Core web app on their rootfs and call it a day — only to discover that they’ve completely run out of RAM, or their app takes more than five minutes to launch, or they discover that Node.js can’t even be compiled for the ARM9 processor they’ve been designing around.

许多熟悉传统 Linux 服务器/桌面开发的开发者认为,他们只需将一个.NET Core 网页应用程序放到他们的根文件系统中就可以了——结果却发现他们的 RAM 完全用完了,或者他们的应用程序启动时间超过五分钟,或者他们发现 Node.js 甚至无法为他们一直设计的 ARM9 处理器编译。💻

The best advice I have is to simply try to run the software you’re interested in using on target hardware and try to characterize the performance as much as possible. Here are some guidelines for where to begin:

我最好的建议就是尽量在目标硬件上运行你感兴趣的软件,并尽可能地对性能进行表征。💻 下面是一些开始的指导原则:📋

- Slower ARM9 cores are for simple headless gadgets written in C/C++. Yes, you can run basic, animation-free low-resolution touch linuxfb apps with these, but blending and other advanced 2D graphics technology can really bog things down.

较慢的 ARM9 内核适用于简单的无头设备,这些设备是用 C/C++编写的。🖥️ 是的,您可以在这些设备上运行基本的、没有动画的低分辨率触控 Linux 帧缓冲应用,但融合和其他高级 2D 图形技术确实会拖慢性能。🎨

And yes, you can run very simple Python scripts, but in my testing, even a “Hello, World!” Flask app took 38 seconds from launch to actually spitting out a web page to my browser on a 300 MHz ARM9.

是的,您可以运行非常简单的 Python 脚本,但在我的测试中,即使是一个“你好,世界!”的 Flask 应用程序,从启动到实际向我的浏览器输出网页也花了 38 秒,运行在一个 300 MHz 的 ARM9 上。🖥️

Yes, obviously once the Python file was compiled, it was much faster, but you should primarily be serving up static content using lightweight HTTP servers whenever possible. And, no, you can’t even compile Node.JS or .NET Core for these architectures.

是的,显然一旦编译了 Python 文件,它会快得多,但你应该尽可能主要使用轻量级 HTTP 服务器来提供静态内容。🚀而且,不,你甚至不能为这些架构编译 Node.JS 或 .NET Core。❌

These also tend to boot from small-capacity SPI flash chips, which limits your framework choices.

这些通常也倾向于从小容量的 SPI 闪存芯片启动,这限制了你的框架选择。⚙️ - Mid-range 500-1000 MHz Cortex-A-series systems can start to support interpreted / JIT-compiled languages better, but make sure you have plenty of RAM — 128 MB is really the bare minimum to consider.

中档的 500-1000 MHz Cortex-A 系列系统可以开始更好地支持解释型/JIT 编译语言,但请确保您有足够的 RAM——128MB 实际上是值得考虑的最低限度。💻

These have no issues running simple C/C++ touch-based GUIs running directly on a framebuffer but can stumble if you want to do lots of SVG rendering, pinch/zoom gestures, and any other canvas work.

这些在直接运行简单的基于 C/C++的触摸 GUI 时没有问题,但如果您想进行大量 SVG 渲染、捏合/缩放手势及其他画布工作时,可能会遇到一些困难。🖥️ - Multi-core 1+ GHz Cortex-A parts with 256 MB of RAM or more will begin to support desktop/server-like deployments. With large eMMC storage (4 GB or more), decent 2D graphics acceleration (or even 3D acceleration on some parts), you can build up complex interactive touchscreen apps using native C/C++ programming, and if the app is simple enough and you have sufficient RAM, potentially using an HTML/JS/CSS-based rendering engine.

多核 1+ GHz Cortex-A 处理器,配备 256 MB 或更多 RAM,将开始支持桌面/服务器级部署。💻 配备大容量 eMMC 存储(4 GB 或更多),良好的 2D 图形加速(甚至在某些部件上提供 3D 加速),您可以使用本地 C/C++编程构建复杂的互动触摸屏应用程序,📱 如果应用程序足够简单且 RAM 充足,可能还可以使用基于 HTML/JS/CSS 的渲染引擎。🌐

If you’re building an Internet-enabled device, you should have no issues doing the bulk of your development in Node.js, .NET Core, or Python if you prefer that over C/C++.

如果你正在构建一个支持互联网的设备,使用 Node.js、.NET Core 或者 Python 进行大部分开发应该没有问题,如果你更喜欢这些而不是 C/C++。💻

What about a Raspberry Pi?

树莓派怎么样?🤖

I know that there are lots of people — especially hobbyists but even professional engineers — who have gotten to this point in the article and are thinking, “I do all my embedded Linux development with Raspberry Pi boards — why do I need to read this?” Yes, Raspberry Pi single-board computers, on the surface, look similar to some of these parts: they run Linux, you can attach displays to them, do networking, and they have USB, GPIO, I2C, and SPI signals available.

我知道有很多人——尤其是爱好者,但甚至还有专业工程师——在本文写到这一点时会想:“我所有的嵌入式 Linux 开发都是用树莓派板做的——我为什么需要读这个?”是的,树莓派单板计算机从表面上看与这些部件有些相似:它们运行 Linux,可以连接显示器,进行网络连接,并且提供 USB、GPIO、I2C 和 SPI 信号。🖥️

And for what it’s worth, the BCM2711 mounted on the Pi 4 is a beast of a processor and would easily best any part in this review on that measure. Dig a bit deeper, though: this processor has video decoding and graphics acceleration, but not even a single ADC input.

值得一提的是,搭载在 Pi 4 上的 BCM2711 处理器性能强劲,轻松超越本评测中的任何组件。🐉 不过,深入探讨一下:这个处理器具备视频解码和图形加速功能,但却没有一个 ADC 输入。🔍

It has built-in HDMI transmitters that can drive dual 4k displays, but just two PWM channels.

它内置了 HDMI 发射器,可以驱动双 4k 显示器,但只有两个 PWM 通道。🎮

This is a processor that was custom-made, from the ground up, to go into smart TVs and set-top boxes — it’s not a general-purpose embedded Linux application processor, so it isn’t generally suited for embedded Linux work.

这是一个从零开始定制的处理器,专为智能电视和机顶盒设计——它不是通用的嵌入式 Linux 应用处理器,因此一般不适合嵌入式 Linux 工作。📺

It might be the perfect processor for your particular project, but it probably isn’t; forcing yourself to use a Pi early in the design process will over-constrain things.

它可能是您特定项目中完美的处理器,但它很可能并不是;在设计过程中早早强迫自己使用树莓派会导致过度限制。💻

Yes, there are always workarounds to the aforementioned shortcomings — like I2C-interfaced PWM chips, SPI-interfaced ADCs, or LCD modules with HDMI receivers — but they involve external hardware that adds power, bulk, and cost. If you’re building a quantity-of-one project and you don’t care about these things, then maybe the Pi is the right choice for the job, but if you’re prototyping a real product that’s going to go into production someday, you’ll want to look at the entire landscape before deciding what’s best.

是的,总有解决上述缺点的变通方法——比如使用 I2C 接口的 PWM 芯片、SPI 接口的 ADC 或带 HDMI 接收器的 LCD 模块——但它们涉及增加电源、体积和成本的外部硬件。如果你正在制作一个单独的项目,并且对这些问题不太在意,那么 Raspberry Pi 可能是适合这个工作的选择;但如果你正在为最终将投入生产的真实产品进行原型开发,那么在决定最佳选择之前,你需要全面了解整个市场情况。📦

A note about peripherals 关于外设的说明📝

This article is all about getting an embedded application processor booting Linux — not building an entire embedded system.

这篇文章主要讲的是如何让一个嵌入式应用处理器启动 Linux,而不是构建整个嵌入式系统。🖥️

If you’re considering running Linux in an embedded design, you likely have some combination of Bluetooth, WiFi, Ethernet, TFT touch screen, audio, camera, or low-power RF transceiver work going on.

如果你正在考虑在嵌入式设计中运行 Linux,那么你可能正在进行一些组合的蓝牙、WiFi、以太网、TFT 触摸屏、音频、摄像头或低功耗射频收发器的工作。📡

If you’re coming from the MCU world, you’ll have a lot of catching up to do in these areas, since the interfaces (and even architectural strategies) are quite different.

如果你是来自 MCU 世界的用户,在这些领域你需要做很多跟进,因为接口(甚至架构策略)是相当不同的。🔧

For example, while single-chip WiFi/BT MCUs are common, very few application processors have integrated WiFi/BT, so you’ll typically use external SDIO- or USB-interfaced chipsets. Your SPI-interfaced ILI9341 TFTs will often be replaced with parallel RGB or MIPI models.

例如,单芯片的 WiFi/蓝牙 MCU 很常见,但很少有应用处理器集成 WiFi/蓝牙,因此您通常会使用外部 SDIO 或 USB 接口的芯片组。您的 SPI 接口的 ILI9341 TFT 通常会被并行 RGB 或 MIPI 模型所替代。📡💻

And instead of burping out tones with your MCU’s 12-bit DAC, you’ll be wiring up I2S audio CODECs to your processor.

而不是使用 MCU 的 12 位 DAC 发出噪音,你将会把 I2S 音频 CODEC 连接到你的处理器上。🔌

我的办公室在过去几个月里完全被这些小型 Linux 开发板淹没了——我总共发送了超过 25 个设计,测试 DDR 布线规则、电源架构,并修复了一些 bug。💻

Hardware Workflow 硬件工作流程 🔧

Processor vendors vigorously encourage reference design modification and reuse for customer designs.

处理器供应商积极鼓励参考设计的修改和再利用,以便于客户的设计。💻

I think most professional engineers are most concerned with getting Rev A hardware that boots up than playing around with optimization, so many custom Linux boards I see are spitting images of off-the-shelf EVKs.

我认为大多数专业工程师更关心的是获得能够启动的 Rev A 硬件,而不是玩优化,因此我看到的许多定制 Linux 板与现成的 EVK 几乎一模一样。🔧

But depending on the complexity of your project, this can become downright absurd.

但根据你项目的复杂性,这可能变得非常荒谬。😅

If you need the massive amount of RAM that some EVKs come with, and your design uses the same sorts of large parallel display and camera interfaces, audio codecs, and networking interfaces on the EVK, then it may be reasonable to use this as your base with little modification.

如果您需要一些开发板配备的大量 RAM,并且您的设计使用相同类型的大型并行显示器和相机接口、音频编解码器以及开发板上的网络接口,那么将其作为基础使用,几乎不作修改,是合理的。💻

However, using a 10-layer stack-up on your simple IoT gateway — just because that’s what the ref design used — is probably not something I’d throw in my portfolio to reflect a shining moment of ingenuity.

然而,在简单的 IoT 网关上使用 10 层堆叠——仅仅因为那是参考设计使用的——可能不是我会放入我的作品集中以体现一个闪耀的创新时刻的东西。💡

People forget that these EVKs are built at substantially higher volumes than prototype hardware is; I often have to explain to inexperienced project managers why it’s going to cost nearly $4000 to manufacture 5 prototypes of something you can buy for $56 each.

人们常常忘记,这些 EVK 的生产量远高于原型硬件的生产量;我经常需要向经验不足的项目经理解释,为什么制造 5 个你可以以每个 56 美元购买的原型,要花近 4000 美元。💵

You may discover that it’s worth the extra time to clean up the design a bit, simplify your stackup, and reduce your BOM — or just start from scratch.

您可能会发现,花额外的时间稍微清理一下设计、简化堆叠并减少 BOM 是值得的——或者干脆从头开始。🛠️

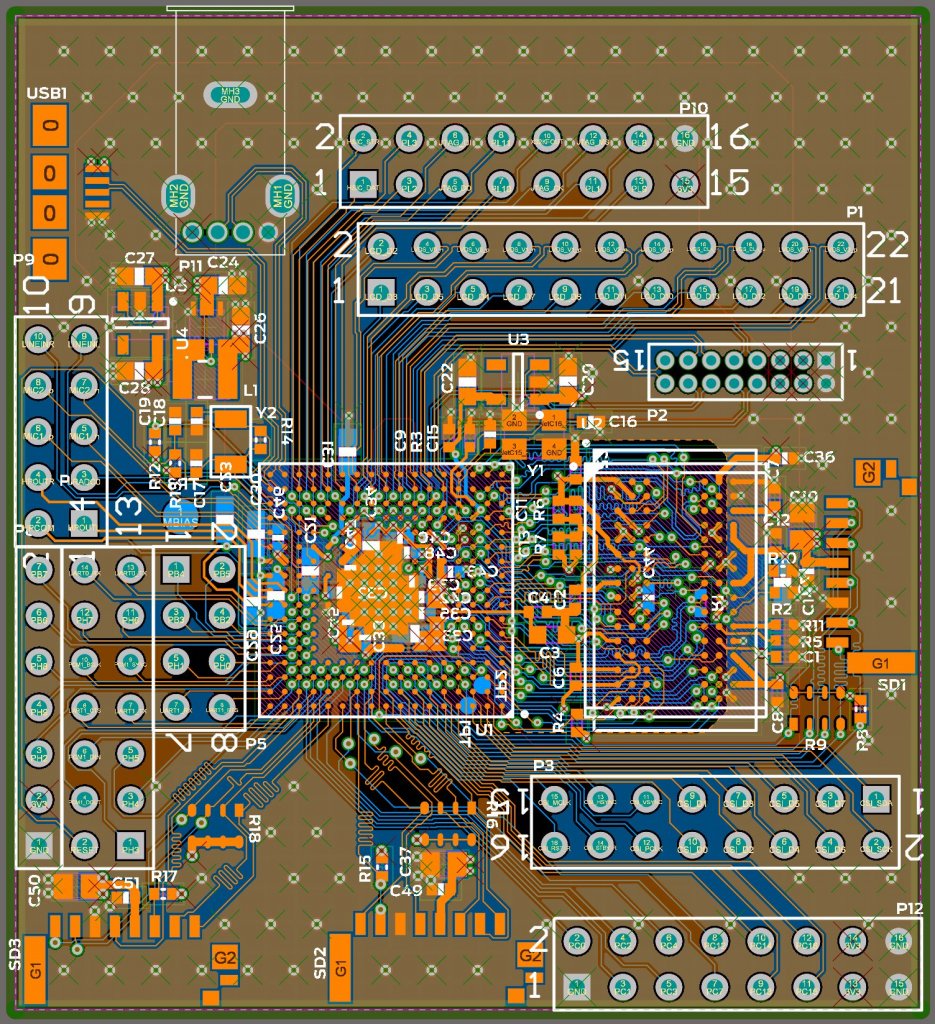

All of the boards I built up for this review were designed in a few days and easily hand-assembled with low-cost hot-plate / hot-air / pencil soldering in a few hours onto cheap 4-layer PCBs from JLC. Even including the cost of assembly labor, it would be hard to spend more than a few hundred bucks on a round of prototypes so long as your design doesn’t have a ton of extraneous circuitry.

我为这次评测组装的所有电路板是在几天内设计的,利用低成本的热板/热风/铅笔焊接,在几个小时内轻松手工组装到 JLC 的便宜四层 PCB 上。即使包括组装劳动力的费用,只要你的设计没有很多多余的电路,花费几百美元做一轮原型也很困难。💰

If you’re just going to copy the reference design files, the nitty-gritty details won’t be important. But if you’re going to start designing from-scratch boards around these parts, you’re going to notice some major differences from designing around microcontrollers.

如果你只是复制参考设计文件,那么细节就不那么重要了。📝 但如果你打算围绕这些组件从零开始设计电路板,你会发现与围绕微控制器设计时有一些重大不同之处。🔍

德州仪器的 AM335x(左侧)具有 0.8mm 间距的满排网格球;而瑞芯微的 RK3308(右侧)则拥有选择性去除的 0.65mm 间距球阵。🔧

BGA Packages BGA 封装💻

Most of the parts in this review come in BGA packages, so we should talk a little bit about this. These seem to make less-experienced engineers nervous — both during layout and prototype assembly.

这篇评论中大多数部件都采用 BGA 封装,所以我们应该稍微谈谈这个。这似乎让经验不足的工程师在布线和原型组装时感到紧张。😟

As you would expect, more-experienced engineers are more than happy to gatekeep and discourage less-experienced engineers from using these parts, but actually, I think BGAs are much easier to design around than high-pin-count ultra-fine-pitch QFPs, which are usually your only other packaging option.

正如你所预期的,经验丰富的工程师非常乐意设立门槛,并且劝阻经验较少的工程师使用这些部件,但实际上,我认为 BGA 的设计比高引脚数超细间距 QFP 要容易得多,而 QFP 通常是你唯一的其他封装选择。🛠️

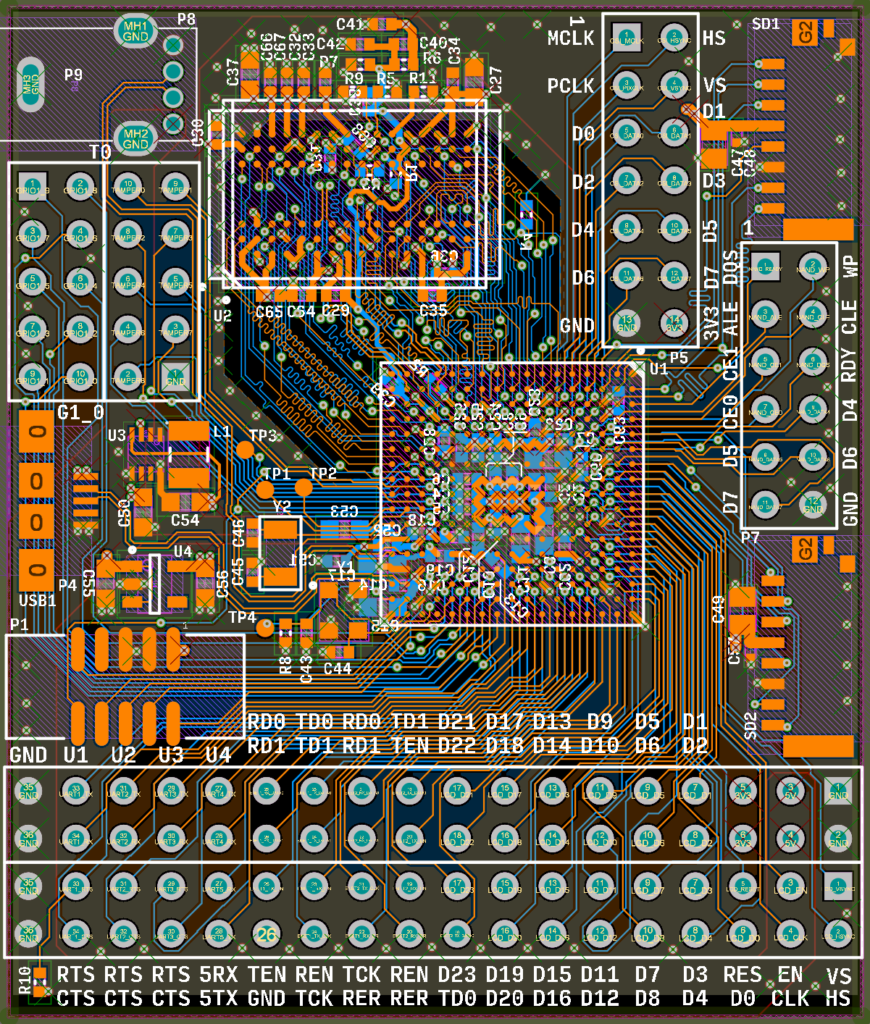

The standard 0.8mm-pitch BGAs that mostly make up this review have a coarse-enough pitch to allow a single trace to pass between two adjacent balls, as well as allowing a via to be placed in the middle of a 4-ball grid with enough room between adjacent vias to allow a track to go between them.

标准的 0.8 毫米间距 BGA 大多构成了本次评审,间距足够大以允许一条单独的引线在两个相邻的焊球之间通过,同时也允许在四球网格的中间放置一个通孔,相邻的通孔之间留有足够的空间以便于引线通过。🛠️

This is illustrated in the image above on the left: notice that the inner-most signals on the blue (bottom) layer escape the BGA package by traveling between the vias used to escape the outer-most signals on the blue layer.

如上图左侧所示:注意到蓝色(底部)层中最内层的信号通过在蓝色层上用于逃逸最外层信号的通孔之间传输,从 BGA 封装中逃逸。🔧

In general, you can escape 4 rows of signals on a 0.8mm-pitch BGA with this strategy: the first two rows of signals from the BGA can be escaped on the component-side layer, while the next two rows of signals must be escaped on a second layer.

一般来说,您可以使用这种策略在 0.8mm 间距的 BGA 上逃离 4 行信号:BGA 的前两行信号可以在元件侧层逃离,而接下来的两行信号必须在第二层上逃离。📏

If you need to escape more rows of signals, you’d need additional layers. IC designers are acutely aware of that; if an IC is designed for a 4-layer board (with two signal layers and two power planes), only the outer 4 rows of balls will carry I/O signals.

如果您需要传输更多行信号,就需要额外的层。🍃 芯片设计师对此非常清楚;如果一个芯片设计用于四层电路板(有两层信号层和两层电源平面),那么只有外侧的四行球体会携带 I/O 信号。🔌

If they need to escape more signals, they can start selectively depopulating balls on the outside of the package — removing a single ball gives space for three or four signals to fit through.

如果他们需要传输更多信号,可以开始选择性地减少封装外部的球 — 移除一个球可以为三个或四个信号提供空间。⚡

For 0.65mm-pitch BGAs (top right), a via can still (barely) fit between four pins, but there’s not enough room for a signal to travel between adjacent vias; they’re just too close.

对于 0.65mm 间距的 BGA(右上角),在四个引脚之间仍然可以(勉强)放置一个通孔,但相邻通孔之间没有足够的空间让信号传输;它们实在是太靠近了。📏

That’s why almost all 0.65mm-pitch BGAs must have selective depopulations on the outside of the BGA.

这就是为什么几乎所有 0.65mm 间距的 BGA 都必须在 BGA 的外侧进行选择性去除。🔧

You can see the escape strategy in the image on the right is much less orderly — there are other constraints (diff pairs, random power nets, final signal destinations) that often muck this strategy up.

你可以看到右侧图像中的逃逸策略显得杂乱无章——还有其他约束(不同的配对、随机的电源网络、最终的信号目标)经常使这一策略变得复杂。😅

I think the biggest annoyance with BGAs is that decoupling capacitors usually end up on the bottom of the board if you have to escape many of the signals, though you can squeeze them onto the top side if you bump up the number of layers on your board (many solder-down SOMs do this).

我认为 BGA 最大的烦恼是,如果你需要逃避许多信号,去耦电容通常会放在电路板的底部,不过如果你增加电路板的层数,就可以把它们挤到顶部(许多焊接型 SOM 也会这样做)。🛠️

Hand-assembling PCBs with these BGAs on them is a breeze. Because 0.8mm-pitch BGAs have such a coarse pitch, placement accuracy isn’t particularly important, and I’ve never once detected a short-circuit on a board I’ve soldered.

手工组装带有这些 BGA 的 PCB 非常简单。由于 0.8mm 间距的 BGA 有着较大的间距,放置精度并不是特别重要,我从未在自己焊接的电路板上发现过短路。😊

That’s a far cry from 0.4mm-pitch (or even 0.5mm-pitch) QFPs, which routinely have minor short-circuits here and there — mostly due to poor stencil alignment. I haven’t had issues soldering 0.65mm-pitch BGAs, either, but I feel like I have to be much more careful with them.

这与 0.4mm 间距(甚至 0.5mm 间距)QFPs 相去甚远,这些 QFP 通常会发生一些小短路——主要是由于模板对准不良。🛠️

我在焊接 0.65mm 间距的 BGA 时也没有遇到问题,但我觉得我必须更加小心。💡

To actually solder the boards, if you have an electric cooktop (I like the Cuisineart ones), you can hot-plate solder boards with BGAs on them. I have a reflow oven, but I didn’t use it once during this review — instead, I hot-plate the top side of the board, flip it over, paste it up, place the passives on the back, and hit it with a bit of hot air.

要实际焊接电路板,如果你有一个电磁炉(我喜欢 Cuisineart 的),你可以用热板焊接带有 BGA 的电路板。🔥我有一个回流焊炉,但在这次评测中我一次都没有使用它——相反,我是在电路板的顶部热焊,翻过来,贴上胶水,放置被动元件在背面,然后用一点热空气处理。💨

Personally, I wouldn’t use a hot-air gun to solder BGAs or other large components, but others do it all the time. The advantage to hot-plate soldering is that you can poke and nudge misbehaving parts into place during the reflow cycle.

个人来说,我不会用热风枪来焊接 BGA 或其他大组件,但其他人总是这样做。热板焊接的优势在于你可以在回流过程中轻推或调整不听话的部件到位。🔥

I also like to give my BGAs a small tap to force them to self-align if they weren’t already.

我也喜欢给我的 BGA 轻轻一敲,以迫使它们自我对齐,如果它们还没有的话。🔧

Multiple voltage domains 多个电压域 ⚡

Microcontrollers are almost universally supplied with a single, fixed voltage (which might be regulated down internally), while most microprocessors have a minimum of three voltage domains that must be supplied by external regulators: I/O (usually 3.3V), core (usually 1.0-1.2V), and memory (fixed for each technology — 1.35V for DDR3L, 1.5V for old-school DDR3, 1.8V for DDR2, and 2.5V for DDR).

微控制器几乎普遍采用单一的固定电压(可能在内部进行了调节),而大多数微处理器则至少有三个电压域必须由外部稳压器供电: I/O(通常为 3.3V),核心(通常为 1.0-1.2V)和内存(根据每种技术固定 — DDR3L 为 1.35V,老式 DDR3 为 1.5V,DDR2 为 1.8V,DDR 为 2.5V)。⚡️

There are often additional analog supplies, and some higher-performance parts might have six or more different voltages you have to supply.

通常会有额外的模拟电源,一些高性能部件可能需要您提供六种或更多不同的电压。⚡

While many entry-level parts can be powered by a few discrete LDOs or DC/DC converters, some parts have stringent power-sequencing requirements.

虽然许多入门级的组件可以通过几个独立的 LDO 或 DC/DC 转换器供电,但有些组件对电源排序有严格的要求。🔋

Also, to minimize power consumption, many parts recommend using dynamic voltage scaling, where the core voltage is automatically lowered when the CPU idles and lowers its clock frequency.

此外,为了降低功耗,许多

These two points lead designers to I2C-interfaced PMIC (power management integrated circuit) chips that are specifically tailored to the processor’s voltage and sequencing requirements, and whose output voltages can be changed on the fly.

这两个要点使设计师们选择了 I2C 接口的 PMIC(电源管理集成电路)芯片,这些芯片专门针对处理器的电压和序列需求进行了调整,并且其输出电压可以实时更改。⚡

These chips might integrate four or more DC/DC converters, plus several LDOs. Many include multiple DC inputs along with built-in lithium-ion battery charging.

这些芯片可能集成四个或更多的直流/直流转换器,以及多个线性稳压器(LDO)。许多芯片包括多个直流输入,并配有内置锂离子电池充电功能。⚡

Coupled with the large inductors, capacitors, and multiple precision resistors some of these PMICs require, this added circuitry can explode your bill of materials (BOM) and board area.

与这些 PMIC 所需的大型电感、电容和多个精密电阻相结合,这些额外的电路可能会大幅增加你的材料清单(BOM)和电路板面积。💥

Regardless of your voltage regulator choices, these parts gesticulate wildly in their power consumption, so you’ll need some basic PDN design ability to ensure you can supply the parts with the current they need when they need it.

无论你选择什么类型的电压调节器,这些元件在功耗方面的变化都非常明显,因此你需要一些基本的 PDN 设计能力,以确保能在需要时为这些元件提供所需的电流。⚡

And while you won’t need to do any simulation or verification just to get things to boot, if things are marginal, expect EMC issues down the road that would not come up if you were working with simple microcontrollers.

虽然你不需要进行任何仿真或验证就能启动,但如果性能边缘,预计将来会出现 EMC 问题,而这些问题在使用简单微控制器时不会出现。🔧

Non-volatile storage 非易失性存储器🗄️

No commonly-used microprocessor has built-in flash memory, so you’re going to need to wire something up to the MPU to store your code and persistent data.

没有常用的微处理器内置闪存,因此您需要将某些东西连接到 MPU,以存储您的代码和持久数据。💻

If you’ve used parts from fabless companies who didn’t want to pay for flash IP, you’ve probably gotten used to soldering down an SPI NOR flash chip, programming your hex file to it, and moving on with your life.

如果你使用过那些不想为闪存 IP 付费的无晶圆厂公司的部件,你可能已经习惯了焊接一个 SPI NOR 闪存芯片,将十六进制文件烧录到上面,然后继续你的生活。💻

When using microprocessors, there are many more decisions to consider.

在使用微处理器时,还有许多其他决策需要考虑。💡

Digi-Key 的内存价格从 16MB 到 64GB,按内存技术颜色编码📊

Most MPUs can boot from SPI NOR flash, SPI NAND flash, parallel, or MMC (for use with eMMC or MicroSD cards). Because of its organization, NOR flash memory has better read speeds but worse write speeds than NAND flash.

大多数 MPU 可以从 SPI NOR 闪存、SPI NAND 闪存、并行接口或 MMC(用于 eMMC 或 MicroSD 卡)启动。😄由于其结构,NOR 闪存的读取速度比 NAND 闪存更快,但写入速度更慢。📉

SPI NOR flash memory is widely used for tiny systems with up to 16 MB of storage, but above that, SPI NAND and parallel-interfaced NOR and NAND flash become cheaper.

SPI NOR 闪存广泛应用于存储容量高达 16 MB 的微型系统,但超过这个容量后,SPI NAND 和并行接口的 NOR 和 NAND 闪存变得更加便宜。💾

Parallel-interfaced NOR flash used to be the ubiquitous boot media for embedded Linux devices, but I don’t see it deployed as much anymore — even though it can be found at sometimes half the price of SPI flash.

并行接口的 NOR 闪存曾是嵌入式 Linux 设备的普遍启动介质,但我发现它现在的应用不如以前了——即使它有时价格仅为 SPI 闪存的一半。💾

My only explanation for its unpopularity is that no one likes wasting lots of I/O pins on parallel memory.

我唯一能解释其不受欢迎的原因是,没有人喜欢在并行内存上浪费大量的 I/O 引脚。🛠️

Above 1 GB, MMC is the dominant technology in use today.

在 1GB 以上,MMC 是目前主流使用的技术。📱

For development work, it’s especially hard to beat a MicroSD card — in low volumes they tend to be cheaper per gigabyte than anything else out there, and you can easily read and write to them without having to interact with the MPU’s USB bootloader; that’s why it was my boot media of choice on almost all platforms reviewed here.

对于开发工作来说,MicroSD 卡几乎无人能敌——在较小的数量中,它们的每千兆字节成本往往比其他任何存储介质都要便宜,而且你可以轻松地读取和写入,无需与 MPU 的 USB 引导加载程序交互;这就是为什么它是我在这里评测的几乎所有平台上的首选启动介质。💾

In production, you can easily switch to eMMC, which is, very loosely speaking, a solder-down version of a MicroSD card.

在生产中,你可以轻松切换到 eMMC,松散地说,它是 MicroSD 卡的一种焊接版本。🔄

Booting 启动 🚀

Back when parallel-interfaced flash memory was the only game in town, there was no need for boot ROMs: unlike SPI or MMC, these devices have address and data pins, so they are easily memory-mapped; indeed, older processors would simply start executing code straight out of parallel flash on reset.

在并行接口闪存还是唯一选择的时候,根本不需要启动 ROM:与 SPI 或 MMC 不同,这些设备拥有地址和数据引脚,因此它们易于进行内存映射;实际上,旧款处理器在重置后会直接开始执行并行闪存中的代码。💾

That’s all changed though: modern application processors have boot ROM code baked into the chip to initialize the SPI, parallel, or SDIO interface, load a few pages out of flash memory into RAM, and start executing it.

不过这一切都改变了:现代应用处理器在芯片中内置了启动 ROM 代码,以初始化 SPI、并行或 SDIO 接口,将几页闪存中的内容加载到 RAM 中,并开始执行。🔧

Some of these ROMs are quite fancy, actually, and can even load files stored inside a filesystem on an MMC device. When building embedded hardware around a part, you’ll have to pay close attention to how to configure this boot ROM.

这些 ROM 实际上相当高级,甚至可以加载存储在 MMC 设备文件系统中的文件。🔧 当围绕一个部件构建嵌入式硬件时,你需要密切关注如何配置这个引导 ROM。📦

While some microprocessors have a basic boot strategy that simply tries every possible flash memory interface in a specified order, others have extremely complicated (“flexible”?) boot options that must be configured through one-time-programmable fuses or GPIO bootstrap pins.

一些微处理器具有基本的启动策略,按照指定的顺序简单地尝试每个可能的闪存接口,而另一些则具有极其复杂的(“灵活的”?)启动选项,这些选项必须通过一次性可编程保险丝或 GPIO 引导引脚进行配置。🔧

And no, we’re not talking about one or two signals you need to handle: some parts have more than 30 different bootstrap signals that must be pulled high or low to get the part booting correctly.

而且,不,我们不是在谈论你需要处理一两个信号:有些部件有超过 30 个不同的引导信号,必须拉高或拉低才能使该部件正确启动。🔧

Console UART 控制台 UART 💻

Unlike MCU-based designs, on an embedded Linux system, you absolutely, positively, must have a console UART available. Linux’s entire tracing architecture is built around logging messages to a console, as is the U-Boot bootloader.

与基于 MCU 的设计不同,在嵌入式 Linux 系统中,您绝对必须有一个可用的控制台 UART。🌟 Linux 的整个追踪架构是围绕将消息记录到控制台而构建的,U-Boot 引导加载程序也是如此。💻

That doesn’t mean you shouldn’t also have JTAG/SWD access, especially in the early stage of development when you’re bringing up your bootloader (otherwise you’ll be stuck with printf() calls).

这并不意味着你不应该拥有 JTAG/SWD 访问权限,尤其是在开发初期,当你在启动引导程序时(否则你将只能使用 printf() 调用)。📡

Having said that, if you actually have to break out your J-Link on your embedded Linux board, it probably means you’re having a really bad day. While you can attach a debugger to an MPU, getting everything set up correctly is extremely clunky when compared to debugging an MCU.

说到这里,如果你实际上需要在嵌入式 Linux 板上使用 J-Link,那可能意味着你正经历一个非常糟糕的一天。🤖 尽管你可以将调试器连接到 MPU,但与调试 MCU 相比,正确设置一切是非常繁琐的。🛠️

Prepare to relocate symbol tables as your code transitions from SRAM to main DRAM memory. It’s not uncommon to have to muck around with other registers, too (like forcing your CPU out of Thumb mode).

准备在代码从 SRAM 切换到主 DRAM 内存时重新定位符号表。💻 处理其他寄存器也是很常见的事情(比如强制你的 CPU 退出 Thumb 模式)。🔧

And on top of that, I’ve found that some U-Boot ports remux the JTAG pins (either due to alternate functionality or to save power), and the JTAG chains on some parts are quite complex and require using less-commonly used pins and features of the interface.

而且,我发现某些 U-Boot 移植会重新映射 JTAG 引脚(要么是由于其他功能,要么是为了节省功耗),并且某些芯片上的 JTAG 链非常复杂,需要使用不常用的引脚和接口特性。🔌

Oh, and since you have an underlying Boot ROM that executes first, JTAG adapters can screw that up, too.

哦,并且由于你有一个首先执行的底层引导 ROM,JTAG 适配器也可能会搞砸这一点。🔧

当前 Digi-Key 的定价趋势显示,512 MB DDR3 / DDR3L 内存是性价比最高的选择,而单芯片的 1 GB 和 2 GB 选项需要支付 30%的溢价。💰

Sidebar: Gatekeepers and the Myth of DDR Routing Complexity

侧边栏:守门人和 DDR 路由复杂性的神话 🛡️

If you start searching around the Internet, you’ll stumble upon a lot of posts from people asking about routing an SDRAM memory bus, only to be discouraged by “experts” lecturing them on how unbelievably complex memory routing is and how you need a minimum 6-layer stack-up and super precise length-tuning and controlled impedances and $200,000 in equipment to get a design working.

如果你开始在互联网上搜索,你会发现很多人发帖询问如何设计 SDRAM 内存总线,结果却被一些“专家”劝退,他们在讲述内存布线是多么复杂,以及你需要至少 6 层的堆叠、超精确的长度调节、受控的阻抗,以及需要 20 万美元的设备才能使设计正常工作。💻

That’s utter bullshit. In the grand scheme of things, routing memory is, at worst, a bit tedious. Once you’ve had some practice, it should take about an hour or so to route a 16-bit-wide single-chip DDR3 memory bus, so I’d hardly call it an insurmountable challenge.

这完全是胡扯。在大局上,布线内存最多也就是有点繁琐。🕒 一旦你有了一些实践经验,布线一个 16 位宽的单芯片 DDR3 内存总线大概需要一个小时左右,所以我根本不认为这是一项无法克服的挑战。💪

It’s worth investing a bit of time to learn about it since it will give you immense design flexibility when architecting your system (since you won’t be beholden to expensive SoMs or SiP-packaged parts).

值得花一点时间去了解它,因为在构建系统时,它会给你带来巨大的设计灵活性(因为你不必依赖昂贵的系统模块或系统级封装部件)。💡

Let’s get one thing straight: I’m not talking about laying out a 64-bit-wide quad-bank memory bus with 16 chips on an 8-layer stack-up. Instead, we’re focused on a single 16-bit-wide memory chip routed point-to-point with the CPU.

让我们先搞清楚一点:我并不是在谈论设计一个 64 位宽、16 个芯片的四银行内存总线,层数为 8 层。相反,我们关注的是一个 16 位宽的单芯片内存,采用点对点的方式与 CPU 连接。💻

This is the layout strategy you’d use with all the parts in this review, and it is drastically simpler than multi-chip layouts — no address bus terminations, complex T-topology routes, or fly-by write-leveling to worry about.

这是您在本次评审中使用的布局策略,它比多芯片布局简单得多——不需要担心地址总线终端、复杂的 T 型拓扑线路或飞翔写入均衡。📐

And with modern dual-die DRAM packages, you can get up to 2 GB capacity in a single DDR3L chip. In exchange for the markup you’ll pay for the dual-die chips, you’ll end up with much easier PCB routing.

现代双芯片 DRAM 封装可以让您在单个 DDR3L 芯片中获得高达 2GB 的容量。💾 作为购买双芯片的溢价回报,您将能够更轻松地进行 PCB 布线。🛠️

Length Tuning 长度调节 🔧

When most people think of DDR routing, length-tuning is the first thing that comes to mind. If you use a decent PCB design package, setting up length-tuning rules and laying down meandered routes is so trivial to do that most designers don’t think anything of it — they just go ahead and length-match everything that’s relatively high-speed — SDRAM, SDIO, parallel CSI / LCD, etc. Other than adding a bit of design time, there’s no reason not to maximize your timing margins, so this makes sense.

当大多数人想到 DDR 布线时,长度调节是首先浮现在脑海中的事情。🛠️如果你使用一个不错的 PCB 设计软件,设置长度调节规则和绘制曲折走线路径是非常简单的,因此大多数设计师对此并不在意——他们只是继续对相对高速的全部线路进行长度匹配——SDRAM、SDIO、并行 CSI / LCD 等。📏除了增加一些设计时间外,没有理由不去最大化你的时序余量,所以这样做是合乎逻辑的。🔍

But what if you’re stuck in a crappy software package, manually exporting spreadsheets of track lengths, manually determining matching constraints, and — gasp — maybe even manually creating meanders? Just how important is length-matching? Can you get by without it?

但如果你被困在一个糟糕的软件包中,手动导出轨道长度的电子表格,手动确定匹配约束,甚至 — 喘气 — 也许还要手动创建蜿蜒路径呢?长度匹配到底有多重要?没有它可以过得去吗?😱

Most microprocessors reviewed here top out at DDR3-800, which has a bit period of 1250 ps. Slow DDR3-800 memory might have a data setup time of up to 165 ps at AC135 levels, and a hold time of 150 ps. There’s also a worst-case skew of 200 ps.

这里审查的大多数微处理器的最高频率为 DDR3-800,其位周期为 1250 皮秒。😌 缓慢的 DDR3-800 内存在 AC135 水平下的数据准备时间可能高达 165 皮秒,保持时间为 150 皮秒。📊 还有最坏情况下的偏移时间为 200 皮秒。⚠️

Let’s assume our microprocessor has the same specs. That means we have 200 ps of skew from our processor + 200 ps of skew from our DRAM chip + 165 ps setup time + 150 ps of hold time = 715 ps total. That leaves a margin of 535 ps (more than 3500 mil!) for PCB length mismatching.

假设我们的微处理器具有相同的规格。🖥️这意味着我们有来自处理器的 200 ps 的偏差 + 来自 DRAM 芯片的 200 ps 的偏差 + 165 ps 的建立时间 + 150 ps 的保持时间 = 总共 715 ps。📏这为 PCB 长度不匹配留出了 535 ps 的裕度(超过 3500 mil!)。📐

i.MX 6UL 的修订历史显示,NXP 实际上移除了 DDR 存储控制器的时序参数。🕒

Are our assumptions about the MPU’s memory controller valid? Who knows. One issue I ran into is that there’s a nebulous cloud surrounding the DDR controllers on many application processors. Take the i.MX 6UL as an example: I discovered multiple posts where people add up worst-case timing parameters in the datasheet, only to end up with practically no timing margin. These official datasheet numbers seem to be pulled out of thin air — so much so that NXP literally removed the entire DDR section in their datasheet and replaced it with a boiler-plate explanation telling users to follow the “hardware design guidelines.” Texas Instruments and ST also lack memory controller timing information in their documentation — again, referring users to stringent hardware design rules.

我们对 MPU 内存控制器的假设是否有效?谁知道呢🤔。我遇到的一个问题是,许多应用处理器上的 DDR 控制器都笼罩着一层模糊的云雾☁️。以 i.MX 6UL 为例:我发现有多篇帖子,大家在数据手册中相加最坏情况的时序参数,结果几乎没有时序裕量😞。这些官方数据手册上的数字似乎完全是凭空而来——以至于 NXP 真的将其数据手册中的整个 DDR 部分删除,替换为一段标准文本,告诉用户遵循“硬件设计指南”📜。德州仪器和 ST 在它们的文档中也缺乏内存控制器的时序信息——同样是让用户遵循严格的硬件设计规则🔧。

((Rockchip and Allwinner don’t specify any sort of timing data or length-tuning guidelines for their processors at all.))

Rockchip 和 Allwinner 完全没有为他们的处理器指定任何类型的时序数据或长度调整指南。🕒

How stringent are these rules? Almost all of these companies recommend a ±25-mil match on each byte group. Assuming 150 ps/cm propagation delay, that’s ±3.175 ps — only 0.25% of that 1250ps DDR3-800 bit period. That’s absolutely nuts.

这些规则有多严格?几乎所有这些公司都建议每个字节组匹配±25 毫英寸。💡假设传播延迟为 150 皮秒/厘米,那就是±3.175 皮秒——仅占 1250 皮秒 DDR3-800 位周期的 0.25%。😲这简直太疯狂了。

Imagine if you were told to ensure your breadboard wires were all within half an inch in length of each other before wiring up your Arduino SPI sensor project — that’s the equivalent timing margin we’re talking about.

想象一下,如果有人告诉你在给你的 Arduino SPI 传感器项目接线之前,确保你的面包板电线长度相差不超过半英寸——这就是我们所说的相当于的时间裕度。🕒

To settle this, I empirically tested two DDR3-800 designs — one with and one without length tuning — and they performed identically. In neither case was I ever able to get a single bit error, even after thousands of iterations of memory stress-tests.

为了验证这一点,我通过实验证明了两种 DDR3-800 设计——一种带有长度调节,一种不带——它们的性能完全相同。在这两种情况下,我都没有遇到过任何比特错误,即使经过了数千次的内存压力测试。🔍

Yes, that doesn’t prove that the design would run for 24/7/365 without a bit error, but it’s definitely a start. Just to verify I wasn’t on the margin, or that this was only valid for one processor, I overclocked a second system’s memory controller by two times — running a DDR3-800 controller at DDR3-1600 speeds — and I was still unable to get a single bit error.

是的,这并不能证明该设计可以 24/7/365 地运行而不出现位错误,但这绝对是一个开始。为确保我不是在临界区域,或者此结果仅适用于一台处理器,我将第二套系统的内存控制器超频了两倍——将 DDR3-800 控制器以 DDR3-1600 的速度运行——但我仍然没有遇到任何位错误。💻

In fact, all five of my discrete-SDRAM-based designs violated these length-matching guidelines and all five of them completed memory tests without issue, and in all my other testing, I never experienced a single crash or lock-up on any of these boards.

事实上,我的五个基于离散 SDRAM 的设计都违反了这些长度匹配指南,但它们全部顺利完成了内存测试,而且在我进行的其他所有测试中,这些电路板没有出现过一次崩溃或卡死。💻

My take-away: length-tuning is easy if you have good CAD software, and there’s no reason not to spend an extra 30 minutes length-tuning things to maximize your timing budget.

我的收获是:如果你有好的 CAD 软件,调节长度是很简单的,没有理由不花多 30 分钟调整长度,以最大化你的时间预算。🛠️

But if you use crappy CAD software or you’re rushing to get a prototype out the door, don’t sweat it — especially for Rev A.

但是如果你使用劣质的 CAD 软件或者急于推出原型,不用担心——特别是对于 Rev A。😅

More importantly, a corollary: if your design doesn’t work, length-tuning is probably the last thing you should be looking at. For starters, make sure you have all the pins connected properly — even if the failures appear intermittent. For example, accidentally swapping byte lane strobes / masks (like I’ve done) will cause 8-bit operations to fail without affecting 32-bit operations. Since the bulk of RAM accesses are 32-bit, things will appear to kinda-sorta work.

更重要的是,一个推论:如果你的设计不起作用,长度调整可能是你最后应该关注的事情。🔧 首先,确保所有引脚都正确连接——即使故障看起来是间歇性的。🔌 例如,意外地交换字节通道的时钟/掩码(就像我做过的那样)会导致 8 位操作失败,而不影响 32 位操作。📉 由于大部分内存访问是 32 位的,事情会看起来有点儿正常。💻

这个眼图显示了一个经过紧密长度调谐的单一数据组,但信号完整性较差。 🟢 阻挡信号用绿色表示,这是从 DRAM 芯片的芯片上查看的。

The blue eye mask shows the AC175-level setup and hold times around the clock transition point for DDR3L memory binned for DDR3-800 operation.

蓝色眼罩显示了针对 DDR3-800 操作的 DDR3L 内存在时钟转换点的 AC175 级别设置和保持时间。🕒

Signal Integrity 信号完整性 📶

Instead of worrying about length-tuning, if a design is failing (either functionally or in the EMC test chamber), I would look first at power distribution and signal integrity.

与其担心长度调谐,不如先关注电源分配和信号完整性,如果设计失败(无论是功能上还是在 EMC 测试室中)。🔧

I threw together some HyperLynx simulations of various board designs with different routing strategies to illustrate some of this.

我结合了一些 HyperLynx 模拟,展示了不同布线策略的多种电路板设计,以说明一些相关内容。💻

I’m not an SI expert, and there are better resources online if you want to learn more practical techniques; for more theory, the books that everyone seems to recommend are by Howard Johnson: High Speed Digital Design: A Handbook of Black Magic and High Speed Signal Propagation: Advanced Black Magic, though I’d also add Henry Ott’s Electromagnetic Compatibility Engineering book to that list.

我不是 SI 专家,如果你想学习更多实用技巧,网上有更好的资源;对于更多理论,大家似乎推荐的书是霍华德·约翰逊的《高速数字设计:黑魔法手册》和《高速信号传播:高级黑魔法》,不过我也会将亨利·奥特的《电磁兼容工程》一书加入到这个名单中。📚

Ideally, every signal’s source impedance, trace impedance, and load impedance would match.

理想情况下,每个信号的源阻抗、传输线阻抗和负载阻抗应当匹配。⚡

This is especially important as a trace’s length starts to approach the wavelength of the signal (I think the rule of thumb is 1/20th the wavelength), which will definitely be true for 400 MHz and faster DDR layouts.

这尤其重要,因为当导线的长度接近信号的波长时(我认为经验法则是波长的 1/20),这对于 400 MHz 及更快的 DDR 布局肯定是正确的。📏

Using a proper PCB stack-up (usually a ~0.1mm prepreg will result in a close-to-50-ohm impedance for a 5mil-wide trace) is your first line of defense against impedance issues, and is usually sufficient for getting things working well enough to avoid simulation / refinement.

使用合适的 PCB 叠层(通常约 0.1mm 的预浸料会导致 5mil 宽度的走线接近 50 欧姆的阻抗)是防止阻抗问题的第一道防线,通常足以使系统正常工作,从而避免模拟/优化。📏

For the data groups, DDR3 uses on-die termination (ODT), configurable for 40, 60, or 120 ohm on memory chips (and usually the same or similar on the CPU) along with adjustable output impedance drivers.

对于数据组,DDR3 采用芯片内终端(ODT),可以在内存芯片上配置为 40、60 或 120 欧姆(通常 CPU 上的配置相同或相似),并配有可调输出阻抗驱动器。📊

ODT is only enabled on the receiver’s end, so depending on whether you’re writing data or reading data, ODT will either be enabled on the memory chip, or on the CPU.

ODT 只在接收端启用,因此根据您是写数据还是读数据,ODT 要么在内存芯片上启用,要么在 CPU 上启用。💻

For simple point-to-point routing, don’t worry too much about ODT settings.

对于简单的点对点路由,不用过于担心 ODT 设置。🔧

As can be seen in the above eye diagram, the difference between 33-ohm and 80-ohm ODT terminations on a CPU reading from DRAM is perceivable, but both are well within AC175 levels (the most stringent voltage levels in the DDR3 spec).

从上述眼图可以看出,CPU 从 DRAM 读取时,33 欧姆和 80 欧姆的 ODT 终端之间的差异是可感知的,但它们都在 AC175 等级之内(这是 DDR3 规范中最严格的电压等级)。📊

The BSP for your processor will initialize the DRAM controller with default settings that will likely work just fine.

您的处理器的 BSP 将使用默认设置初始化 DRAM 控制器,这些设置应该可以正常工作。🌟

一个未终止的地址总线,通过慢速斜率设置和 80 欧姆输出驱动器被调整到位。📏 虽然有显著的超调,但低于 DRAM 数据表中的 400mV 规范。📉 信号之间的偏差是由于近 300 毫英寸的长度不匹配造成的。🔧

The biggest source of EMC issues related to DDR3 is likely going to come from your address bus. DDR3 uses a one-way address bus (the CPU is always the transmitter and the memory chip is always the receiver), and DDR memory chips do not have on-chip termination for these signals.

与 DDR3 相关的电磁兼容性(EMC)问题的最大来源很可能来自于你的地址总线。🔌 DDR3 使用单向地址总线(CPU 始终是发送方,内存芯片始终是接收方),并且 DDR 内存芯片对这些信号没有片上终端。🧠

Theoretically, they should be terminated to VTT (a voltage derived from VDDQ/2) with resistors placed next to the DDR memory chip. On large fly-by buses with multiple memory chips, you’ll see these VTT termination resistors next to the last chip on the bus.

理论上,它们应该通过放置在 DDR 内存芯片旁边的电阻接地到 VTT(一个来自 VDDQ/2 的电压)。在多个内存芯片的大型飞线总线上,您会在总线的最后一个芯片旁边看到这些 VTT 终结电阻。📌

The resistors absorb the EM wave propagating from the MPU which reduces the reflections back along the transmission line that all the memory chips would see as voltage fluctuations.

电阻吸收来自 MPU 的电磁波,这减少了在传输线上反射回来的波,所有内存芯片会将其视为电压波动。📡

On small point-to-point designs, the length of the address bus is usually so short that there’s no need to terminate.

在小型点对点设计中,地址总线的长度通常非常短,因此不需要终端。🔌

If you run into EMC issues, consider software fixes first, like using slower slew-rate settings or increasing the output impedance to soften up your signals a bit.

如果你遇到电磁兼容性的问题,首先考虑软件修复,比如使用更慢的率变化设置或增加输出阻抗,以稍微减弱信号。⚡

我们可以通过在信号之间留出足够的空间来减少互耦,但对于单芯片 DRAM 布线来说,这通常是没有必要的,因为走线长度将小于 2 英寸。📏

Another source of SI issues is cross-coupling between traces. To reduce cross-talk, you can put plenty of space between traces — three times the width (3S) is a standard rule of thumb.

另一个 SI 问题的来源是走线之间的串扰。为了减少串扰,您可以在走线之间留出足够的空间——通常是走线宽度的三倍(3S)是一个标准的经验法则。📏

I sound like a broken record, but again, don’t be too dogmatic about this unless you’re failing tests, as the lengths involved with routing a single chip are so short.

我听起来像个老生常谈,但再次提醒,除非你考试不及格,否则不要对此过于死板,因为单个芯片的布线长度非常短。🎶

The above figure illustrates the routing of a DDR bus with no length-tuning but with ample space between traces. Note the eye diagram (below) shows much better signal integrity (at the expense of timing skew) than the first eye diagram presented in this section.

上面的图示说明了一个没有长度调节的 DDR 总线的布线,但信号线之间有足够的间隔。请注意,下面的眼图显示的信号完整性要比本节首次呈现的眼图好得多(尽管牺牲了时序偏差)。📊

3S 路由内存总线的眼图。使用约 50 欧姆微带线时,使用 33 欧姆和 80 欧姆 ODT 终端的区别,输出为 40 欧姆。⚡️

Both are well within stringent AC175 specs, but the 80-ohm shows more overshoot and ringing, while the 30-ohm is unnecessarily overdamped. The skew in the signals is the result of 150mil of length difference between the shortest and longest signals.

两者都在严格的 AC175 规格范围内,但 80 欧姆显示出更多的超调和振铃,而 30 欧姆则过度阻尼。信号的偏差是由于最短和最长信号之间 150 毫的长度差异造成的。📏

Pin Swapping 引脚互换 🔄

Because DDR memory doesn’t care about the order of the bits getting stored, you can swap individual bits — except the least-significant one if you’re using write-leveling — in each byte lane with no issues. Byte lanes themselves are also completely swappable.

因为 DDR 内存不关心存储位的顺序,你可以在每个字节通道中交换单个位——如果使用写入均衡,则最不重要的位除外——而没有任何问题。字节通道本身也是完全可以互换的。💾

Having said that, since all the parts I reviewed are designed to work with a single x16-wide DDR chip (which has an industry-standard pinout), I found that most pins were already balled out reasonably well.

尽管如此,由于我审核的所有部件都是为单个 x16 宽的 DDR 芯片设计的(该芯片具有行业标准的引脚布局),我发现大多数引脚已经合理地进行了引出。🔌

Before you start swapping pins, make sure you’re not overlooking an obvious layout that the IC designers intended.

在开始交换引脚之前,确保你没有忽视集成电路设计师所意图的明显布局。🔄

Recommendations 建议 💡

Instead of worrying about chatter you read on forums or what the HyperLynx salesperson is trying to spin, for simple point-to-point DDR designs, you shouldn’t have any issues if you follow these suggestions:

与其担心你在论坛上看到的闲聊或 HyperLynx 销售人员的推销,不如对简单的点对点 DDR 设计遵循以下建议,这样你就不会遇到任何问题:💡

Pay attention to PCB stack-up. Use a 4-layer stack-up with thin prepreg (~0.1mm) to lower the impedance of your microstrips — this allows the traces to transfer more energy to the receiver. Those inner layers should be solid ground and DDR VDD planes respectively.

注意 PCB 叠层结构。使用四层叠层,薄的预浸料(约 0.1mm)可以降低微带线的阻抗——这样可以使线路更有效地将能量传输到接收器。内层应分别为实心接地层和 DDR VDD 电源层。⚡

Make sure there are no splits under the routes. If you’re nit-picky, pull back the outer-layer copper fills from these tracks so you don’t inadvertently create coplanar structures that will lower the impedance too much.

确保在布线路径下没有分裂。 如果你比较挑剔,拉回这些轨道的外层铜填充,以免无意中创建共面结构,从而降低阻抗过多。 🛤️

Avoid multiple DRAM chips. If you start adding extra DRAM chips, you’ll have to route your address/command signals with a fly-by topology (which requires terminating all those signals — yuck), or a T-topology (which requires additional routing complexity).

避免使用多个 DRAM 芯片。如果你开始添加额外的 DRAM 芯片,你必须以飞行拓扑来布线你的地址/命令信号(这需要终端所有这些信号——真糟糕),或者使用 T 型拓扑(这需要额外的布线复杂性)。💡

Stick with 16-bit-wide SDRAM, and if you need more capacity, spend the extra money on a dual-die chip — you can get up to 2 GB of RAM in a single X16-wide dual-rank chip, which should be plenty for anything you’d throw at these CPUs.

坚持使用 16 位宽的 SDRAM,如果你需要更大的容量,可以花额外的钱购买双晶片芯片——在单个 X16 宽的双排列芯片中,你可以获得高达 2GB 的 RAM,这对于任何你想要使用的这些 CPU 来说应该足够了。🖥️

Faster RAM makes routing easier. Even though our crappy processors reviewed here rarely can go past 400-533 MHz DDR speeds, using 800 or 933 MHz DDR chips will ease your timing budget.

更快的 RAM 使得路由更简单。尽管我们在这里评测的劣质处理器很少能超过 400-533 MHz 的 DDR 速度,使用 800 或 933 MHz 的 DDR 芯片将会减轻你的时序预算。⚡️

The reduced setup/hold times make address/command length-tuning almost entirely unnecessary, and the reduced skew even helps with the bidrectional data bus signals.

减少的设置/保持时间使得地址/命令长度调节几乎完全不必要,而减少的偏斜甚至有助于双向数据总线信号。📉

Software Workflow 软件工作流程 ⚙️

Developing on an MCU is simple: install the vendor’s IDE, create a new project, and start programming/debugging. There might be some .c/.h files to include from a library you’d like to use, and rarely, a precompiled lib you’ll have to link against.

在单片机上开发很简单:安装供应商的集成开发环境,创建一个新项目,然后开始编程/调试。可能需要包含一些你想使用的库中的 .c/.h 文件,偶尔还需要链接一个预编译的库。💻

When building embedded Linux systems, we need to start by compiling all the off-the-shelf software we plan on running — the bootloader, kernel, and userspace libraries and applications.

在构建嵌入式 Linux 系统时,我们需要首先编译所有计划运行的现成软件——引导加载程序、内核以及用户空间库和应用程序。🛠️

We’ll have to write and customize shell scripts and configuration files, and we’ll also often write applications from scratch. It’s really a totally different development process, so let’s talk about some prerequisites.

我们需要编写和定制 shell 脚本和配置文件,通常还会从头开始编写应用程序。这真的是一个完全不同的开发过程,所以让我们谈谈一些前提条件。🛠️

If you want to build a software image for a Linux system, you’ll need a Linux system. If you’re also the person designing the hardware, this is a bit of a catch-22 since most PCB designers work in Windows. While Windows Subsystem for Linux will run all the software you need to build an image for your board, WSL currently has no ability to pass through USB devices, so you won’t be able to use hardware debuggers (or even a USB microSD card reader) from within your Linux system.

如果你想为 Linux 系统构建一个软件镜像,你需要一个 Linux 系统。🖥️ 如果你也是设计硬件的人,这就有点矛盾,因为大多数 PCB 设计师在 Windows 中工作。🔧 虽然 Windows 的 Linux 子系统可以运行你构建板子镜像所需的所有软件,但 WSL 目前没有传递 USB 设备的能力,因此你将无法在 Linux 系统中使用硬件调试器(甚至是 USB microSD 卡读取器)。📱

And since WSL2 is Hyper-V-based, once it’s enabled, you won’t be able to launch VMware, which uses its own hypervisor((Though a beta versions of VMWare will address this)).

由于 WSL2 是基于 Hyper-V 的,一旦启用,您将无法启动使用其自有虚拟机管理程序的 VMware(尽管 VMware 的测试版将解决此问题)。🖥️

Consequently, I recommend users skip over all the newfangled tech until it matures a bit more, and instead just spin up an old-school VMWare virtual machine and install Linux on it.

因此,我建议用户跳过所有新奇的技术,直到它们成熟一些,而是直接启动一个老式的 VMWare 虚拟机并在上面安装 Linux。🖥️

In VMWare you can pass through your MicroSD card reader, debug probe, and even the device itself (which usually has a USB bootloader).

在 VMWare 中,你可以直接传递你的 MicroSD 卡读卡器、调试探针,甚至设备本身(通常具有 USB 引导加载程序)。📦

Building images is a computationally heavy and highly-parallel workload, so it benefits from large, high-wattage HEDT/server-grade multicore CPUs in your computer — make sure to pass as many cores through to your VM as possible.

构建镜像是一个计算量大且高度并行的工作负载,因此可以从计算机中的大型、高功率的 HEDT/服务器级多核 CPU 中受益——确保尽可能将更多核心传递给你的虚拟机。💻

Compiling all the software for your target will also eat through storage quickly: I would allocate an absolute minimum of 200 GB if you anticipate juggling between a few large embedded Linux projects simultaneously.

编译所有针对目标的软件将迅速占用存储空间:如果您预计要同时处理几个大型嵌入式 Linux 项目,我建议至少分配 200 GB 的存储空间。💾

While your specific project will likely call for much more software than this, these are the five components that go into every modern embedded Linux system((Yes, there are alternatives to these components, but the further you move away from the embedded Linux canon, the more you’ll find yourself on your own island, scratching your head trying to get things to work.)):

虽然你的具体项目可能需要更多的软件,但

- A cross toolchain, usually GCC + glibc, which contains your compiler, binutils, and C library. This doesn’t actually go into your embedded Linux system, but rather is used to build the other components.

交叉工具链,通常是 GCC + glibc,其中包含编译器、二进制工具和 C 库。这实际上并不会进入你的嵌入式 Linux 系统,而是用来构建其他组件。🔧 - U-boot, a bootloader that initializes your DRAM, console, and boot media, and then loads the Linux kernel into RAM and starts executing it.

U-boot 是一个引导加载程序,它初始化你的 DRAM、控制台和启动媒体,然后将 Linux 内核加载到内存中并开始执行。🚀 - The Linux kernel itself, which manages memory, schedules processes, and interfaces with hardware and networks.

Linux 内核本身负责管理内存、调度进程,并与硬件和网络进行交互。🖥️ - Busybox, a single executable that contains core userspace components (init, sh, etc)

Busybox,一个包含核心用户空间组件(init、sh 等)的单个可执行文件。🔧 - a root filesystem, which contains the aforementioned userspace components, along with any loadable kernel modules you compiled, shared libraries, and configuration files.

根文件系统,其中包含上述用户空间组件,以及您编译的任何可加载内核模块、共享库和配置文件。📂

As you’re reading through this, don’t get overwhelmed: if your hardware is reasonably close to an existing reference design or evaluation kit, someone has already gone to the trouble of creating default configurations for you for all of these components, and you can simply find and modify them.

在您阅读这篇文章时,不要感到不知所措:如果您的硬件与现有的参考设计或评估板大致相近,那么已经有人为您创建了所有这些组件的默认配置,您只需找到并修改它们即可。📦

As an embedded Linux developer doing BSP work, you’ll spend way more time reading other people’s code and modifying it than you will be writing new software from scratch.

作为一名嵌入式 Linux 开发者,从事 BSP 工作,你将花费更多的时间阅读和修改其他人的代码,而不是从头编写新的软件。🖥️

Cross Toolchain 交叉工具链 🛠️

Just like with microcontroller development, when working on embedded Linux projects, you’ll write and compile the software on your computer, then remotely test it on your target. When programming microcontrollers, you’d probably just use your vendor’s IDE, which comes with a cross toolchain — a toolchain designed to build software for one CPU architecture on a system running a different architecture. As an example, when programming an ATTiny1616, you’d use a version of GCC built to run on your x64 computer but designed to emit AVR code.

就像进行微控制器开发一样,当你在嵌入式 Linux 项目上工作时,你会在计算机上编写和编译软件,然后在目标设备上进行远程测试。💻 当编程微控制器时,你可能只会使用厂商提供的集成开发环境(IDE),其中包含交叉工具链——这是一个旨在在运行不同架构的系统上为一种 CPU 架构构建软件的工具链。🔧 举个例子,当编程 ATTiny1616 时,你会使用一个为你的 x64 计算机构建的 GCC 版本,但它设计用于输出 AVR 代码。📦

With embedded Linux development, you’ll need a cross toolchain here, too (unless you’re one of the rare types coding on an ARM-based laptop or building an x64-powered embedded system).

在嵌入式 Linux 开发中,你也需要一个交叉工具链(除非你是那些稀有的在 ARM 基础笔记本电脑上编码或构建 x64 驱动的嵌入式系统的人)。💻

When configuring your toolchain, there are two lightweight C libraries to consider — musl libc and uClibc-ng — which implement a subset of features of the full glibc, while being 1/5th the size. Most software compiles fine against them, so they’re a great choice when you don’t need the full libc features. Between the two of them, uClibc is the older project that tries to act more like glibc, while musl is a fresh rewrite that offers some pretty impressive stats, but is less compatible.

在配置您的工具链时,有两个轻量级的 C 库需要考虑——musl libc 和 uClibc-ng——它们实现了 glibc 的子集功能,同时体积仅为其 1/5。🔧 大多数软件在它们上编译都很好,因此当您不需要完整的 libc 功能时,它们是一个很好的选择。💡 在它们之间,uClibc 是一个较老的项目,试图更像 glibc,而 musl 则是一个全新的重写,提供了一些相当令人印象深刻的统计数据,但兼容性较差。📊

U-Boot U-Boot 🛠️

Unfortunately, our CPU’s boot ROM can’t directly load our kernel. Linux has to be invoked in a specific way to obtain boot arguments and a pointer to the device tree and initrd, and it also expects that main memory has already been initialized.

不幸的是,我们的 CPU 引导 ROM 无法直接加载我们的内核。😞 Linux 必须以特定的方式调用,以获取引导参数和指向设备树及 initrd 的指针,同时它还期望主内存已经初始化。📦

Boot ROMs also don’t know how to initialize main memory, so we would have nowhere to store Linux. Also, boot ROMs tend to just load a few KB from flash at the most — not enough to house an entire kernel.

引导 ROM 也不知道如何初始化主存储器,所以我们没有地方存储 Linux。🖥️ 此外,引导 ROM 通常最多只从闪存加载几 KB 的数据——这不足以容纳整个内核。📦

So, we need a small program that the boot ROM can load that will initialize our main memory and then load the entire (usually-multi-megabyte) Linux kernel and then execute it.

因此,我们需要一个小程序,启动 ROM 可以加载它,以初始化我们的主存储器,然后加载整个(通常是几兆字节的)Linux 内核,并执行它。💻

The most popular bootloader for embedded systems, Das U-Boot, does all of that — but adds a ton of extra features. It has a fully interactive shell, scripting support, and USB/network booting.

最受欢迎的嵌入式系统引导加载程序,Das U-Boot,完成了所有这些 —— 但增加了大量额外功能。它拥有一个完全交互式的命令行、脚本支持和 USB/网络启动。🔧